©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 59

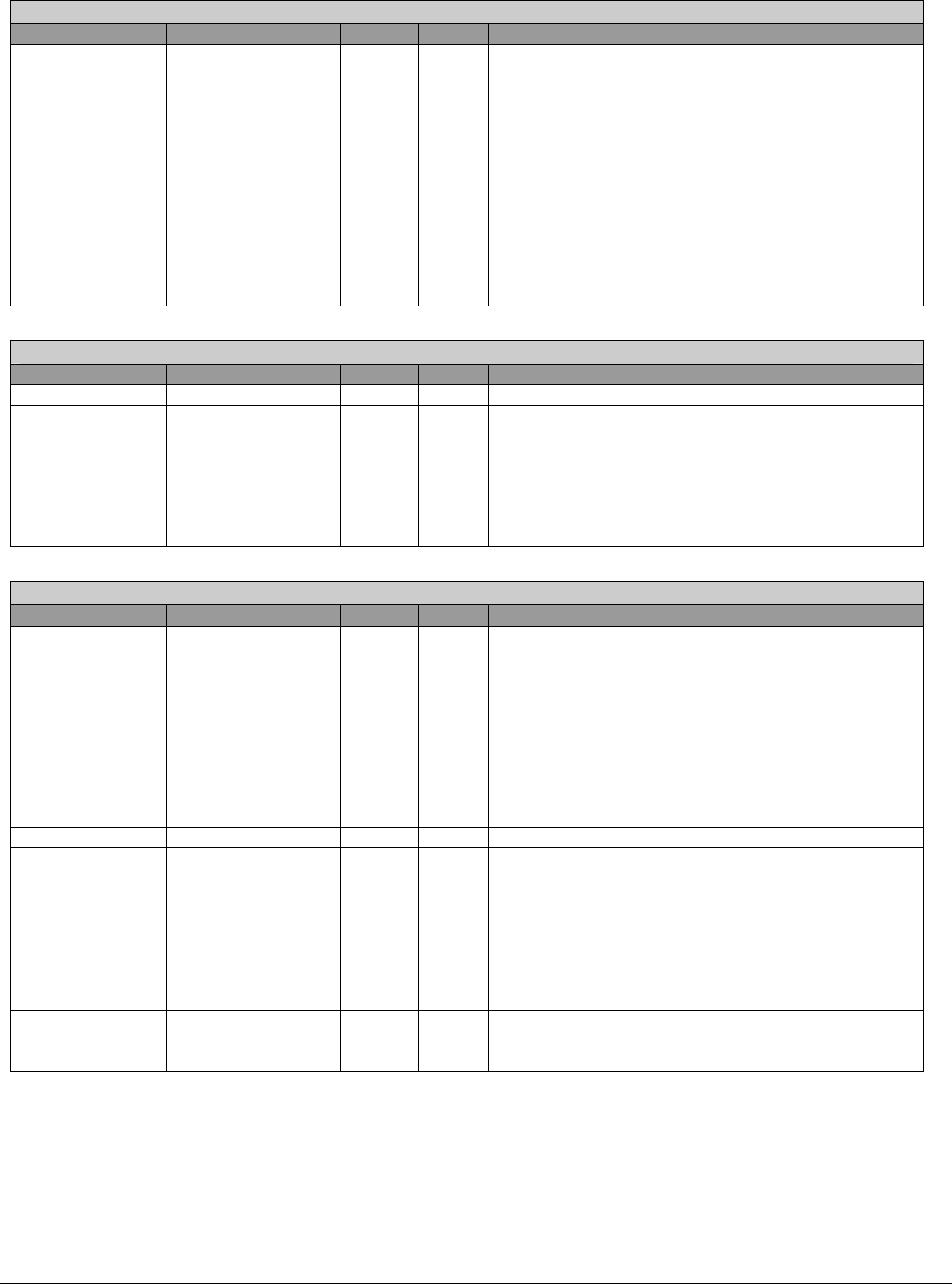

HcBulkCurrentED - 32 bits - [MEM_Reg : 2Ch]

Field Name Bits Default HCD HC Description

BCED 31:4 0000000

h

RW RW

BulkCurrentED

This is advanced to the next ED after the HC has

served the present one. HC continues processing the

list from where it left off in the last Frame. When it

reaches the end of the Bulk list, HC checks the

ControlListFilled of HcControl. If set, it copies the

content of HcBulkHeadED to HcBulkCurrentED and

clears the bit. If it is not set, it does nothing. HCD is

only allowed to modify this register when the

BulkListEnable of HcControl is cleared. When set,

the HCD only reads the instantaneous value of this

register. This is initially set to zero to indicate the end

of the Bulk list.

HcDoneHead - 32 bits - [MEM_Reg : 30h]

Field Name Bits Default HCD HC Description

Reserved 3:0 Reserved

DH 31:4 0b R RW

DoneHead

When a TD is completed, HC writes the content of

HcDoneHead to the NextTD field of the TD. HC then

overwrites the content of HcDoneHead with the

address of this TD. This is set to zero whenever HC

writes the content of this register to HCCA. It also

sets the WritebackDoneHead of HcInterruptStatus.

HcFmInterval - 32 bits - [MEM_Reg : 34h]

Field Name Bits Default HCD HC Description

FI 13:0 2EDFh RW R

FrameInterval

This specifies the interval between two consecutive

SOFs in bit times. The nominal value is set to be

11,999.

HCD should store the current value of this field before

resetting HC. By setting the HostControllerReset

field of HcCommandStatus as this will cause the HC

to reset this field to its nominal value. HCD may

choose to restore the stored value upon the

completion of the Reset sequence.

Reserved 15:14 Reserved

FSMPS 30:16 0000h RW R

FSLargestDataPacket

This field specifies a value which is loaded into the

Largest Data Packet Counter at the beginning of

each frame. The counter value represents the largest

amount of data in bits which can be sent or received

by the HC in a single transaction at any given time

without causing scheduling overrun. The field value is

calculated by the HCD.

FIT 31 0b RW R

FrameIntervalToggle

HCD toggles this bit whenever it loads a new value to

FrameInterval