©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 38

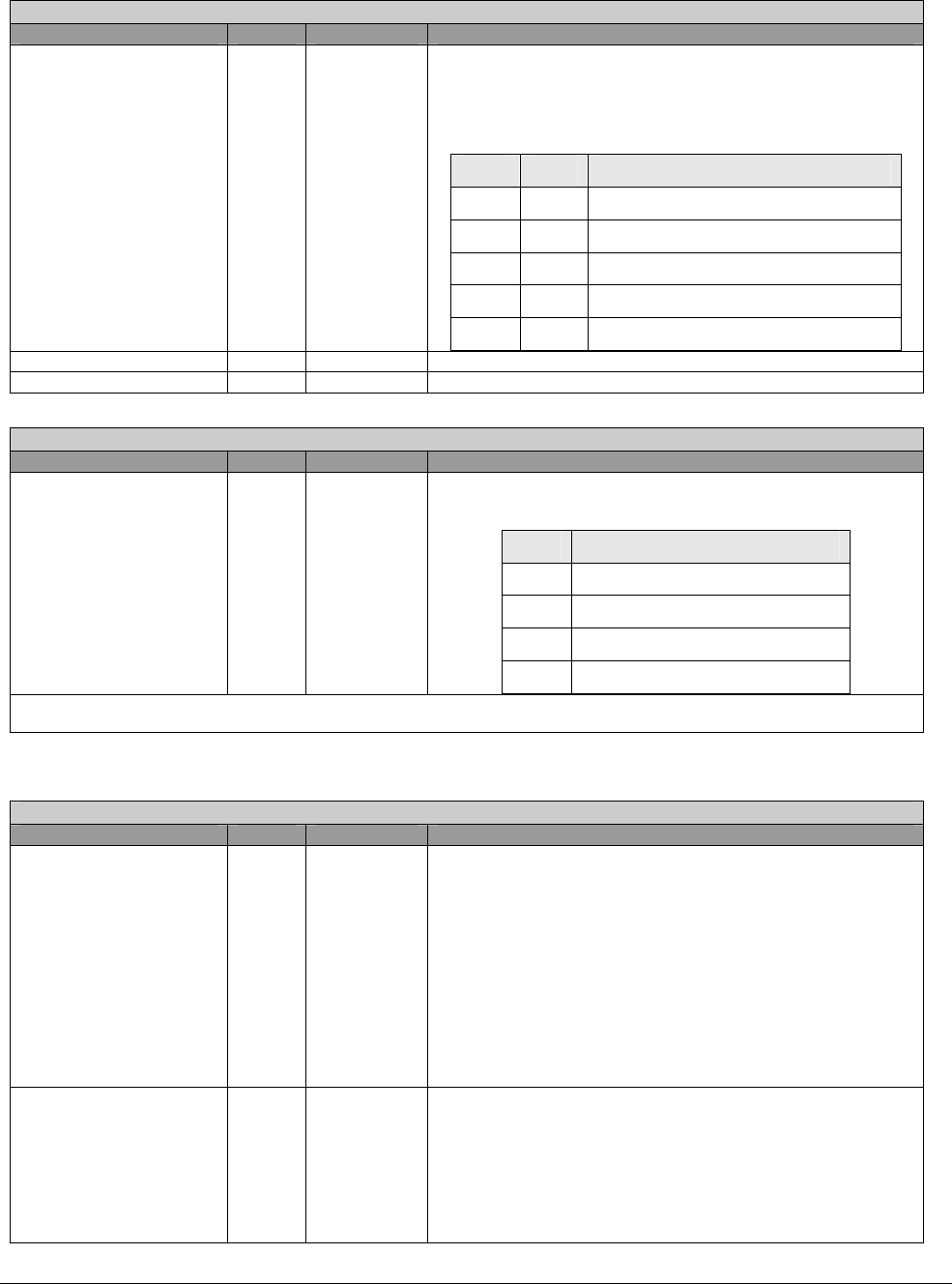

Port-N Task Fike Data – R – 32 bits [Mem_reg: ABAR + port offset + 20h]

Field Name Bits Default Description

Status (STS) 7:0 7Fh

Contains the latest copy of the task file status register. Fields

of note in this register that affect AHCI hardware operation

are:

Bit Field Definition

7 BSY Indicates the interface is busy

6:4 cs Command specific

3 DRQ Indicates a data transfer is requested

2:1 cs Command specific

0 ERR Indicates an error during the transfer.

ERROR 15:8 00h Contains the latest copy of the task file error register.

Reserved 31:16 Reserved

Port-N Signature – R – 32 bits [Mem_reg: ABAR + port offset + 24h]

Field Name Bits Default Description

Signature (SIG) 31:0 FFFFFFFFh

Contains the signature received from a device on the first

D2H Register FIS. The bit order is as follows:

Bit Field

31:24 LBA High Register

23:16 LBA Mid Register

15:08 LBA Low Register

07:00 Sector Count Register

It is updated once after a reset sequence.

Port-N Serial ATA Status – R – 32 bits [Mem_reg: ABAR + port offset + 28h]

Field Name Bits Default Description

Device Detection (DET) 3:0 0h

Indicates the interface device detection and Phy state.

0h No device detected and Phy communication not

established

1h Device presence detected but Phy communication

not established

3h Device presence detected and Phy communication

established

4h Phy in offline mode as a result of the interface

being disabled or running in a BIST loopback mode

All other values reserved. Read Only

Current Interface Speed

(SPD)

7:4 0h

Indicates the negotiated interface communication speed.

0h Device not present or communication not

established

1h Generation 1 communication rate negotiated

2h Generation 2 communication rate negotiated

All other values reserved. Read Only