©2008 Advanced Micro Devices, Inc.

IDE Controller (Device 20, Function 1)

AMD SB600 Register Reference Manual Proprietary Page 193

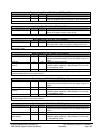

IDE Ultra DMA Status - RW- 8 bits - [PCI_Reg:55h]

Field Name Bits Default Description

IDE Ultra DMA Status Register: This register specifies the Ultra DMA status for primary channel.

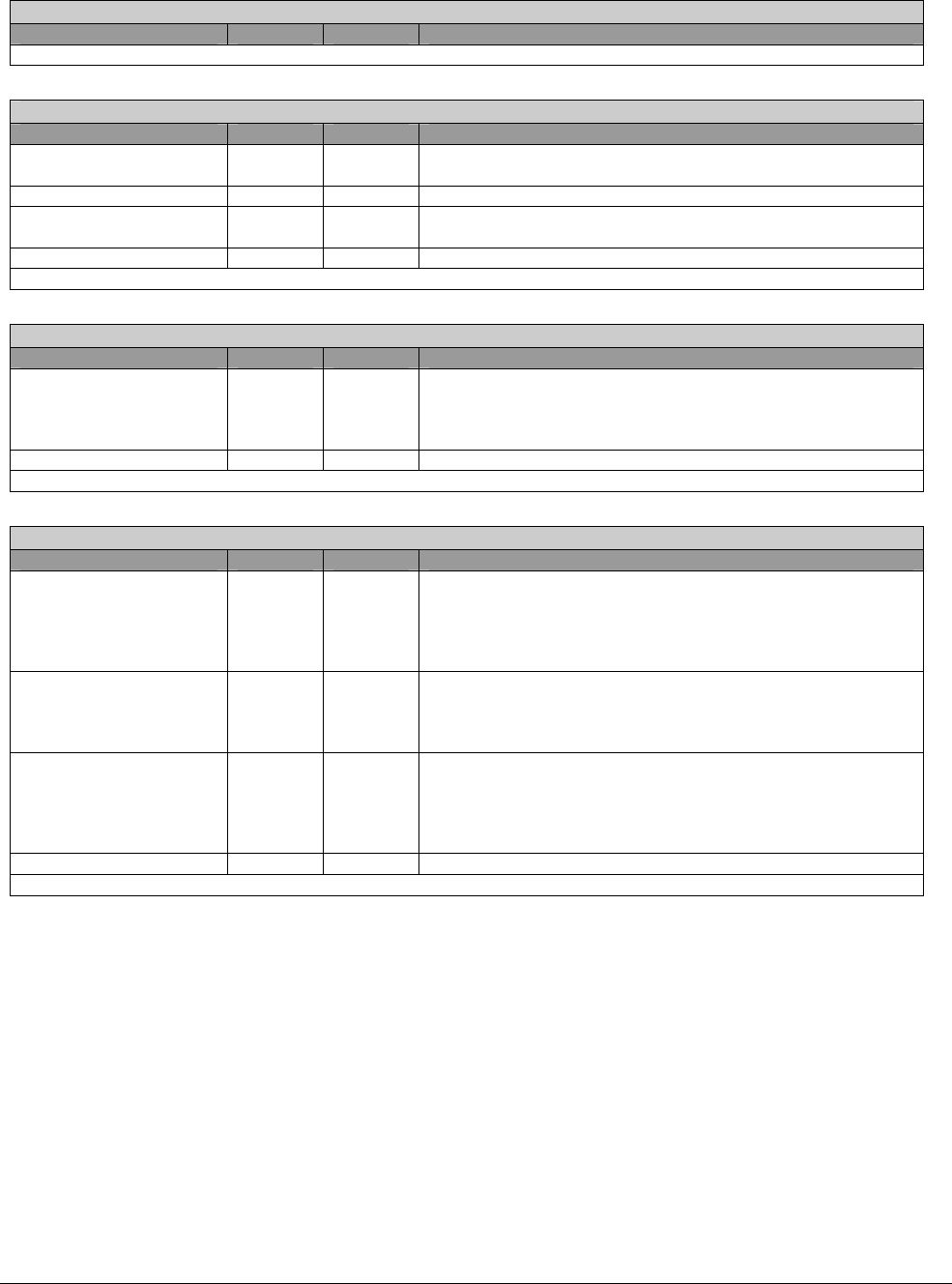

IDE Ultra DMA Mode - RW- 16 bits - [PCI_Reg:56h]

Field Name Bits Default Description

Primary Master Ultra

DMA Access Mode

2:0 0h Ultra DMA access mode for Primary IDE master device. For

instance, UDMA-5 = 101, UDMA-6 = 110.

Reserved 3 0b Reserved. Always read as 0’s.

Primary Slave Ultra DMA

Access Mode

6:4 0h Ultra DMA access mode for Primary IDE Slave device. For

instance, UDMA-5 = 101, UDMA-6 = 110.

Reserved 15:7 000h Reserved. Always wired as 0’s.

IDE Ultra DMA Mode Register: This register specifies the Ultra DMA timings for primary channel.

IDE PCI Retry Timing Counter - RW- 8 bits - [PCI_Reg:60h]

Field Name Bits Default Description

PCI Retry Timing

Counter

3:0 0h Waiting number of PCI clocks. If a PCI Master transaction is

retried, the IDE host controller will wait for 0-15 PCI clocks,

depending upon the value programmed, and will re-issue the

PCI master transaction.

Reserved 7:4 0h Reserved. Always wired as 0’s.

IDE PCI Retry Timing Counter Register: This register specifies the Ultra DMA re-try timings for primary channel.

PCI Error Control - RW- 8 bits - [PCI_Reg:61h]

Field Name Bits Default Description

PCI Data Parity Check

Ignore

0 0b 0 - Check parity bit for DMA transaction.

1 - Ignore parity bit for DMA transaction.

If there is a parity error with a DMA transaction, the IDE

host controller does not set the error bit (Bus Master IDE

Reg.) If this bit is 1, bit 1 is “don’t care.” (same as bit 1=0.)

PCI Descriptor DMA

Abort Enable

1 0b 0 - DMA will not be aborted by PCI parity error at descriptor

table read.

1- DMA will be aborted by PCI parity error at descriptor table

read.

PCI Master/Target Abort

Ignore

2 0b 0 - DMA will be aborted by parity error, master abort, and

target abort at data transaction (if bit0=1 or bit1=0, DMA

does not abort by parity error.)

1 - DMA does not abort by parity error, master abort, and

target abort at data transaction.

Reserved 7:3 00h Reserved. Always wired as 0’s.

PCI Error Control Register: This register specifies DMA parity bit errors.