©2008 Advanced Micro Devices, Inc.

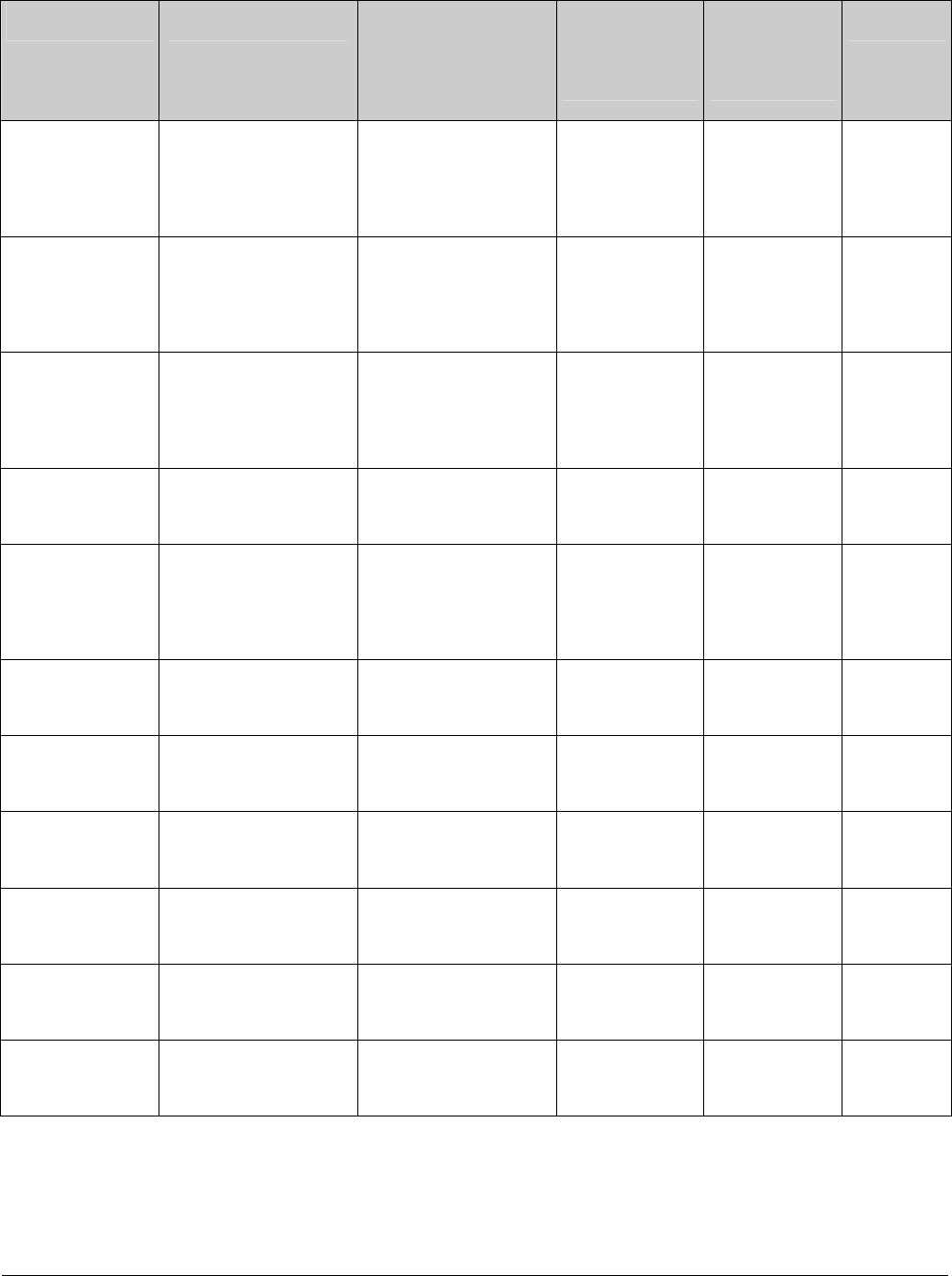

GPIO/GPOC

AMD SB600 Register Reference Manual Proprietary Page 280

Pin Name

(Note 1)

Multi-function

Selection

Output Enable

(On SMBus

Controller)

Bus 00h/ Dev14h/

Fun00

Input if GPI

(On SMBus

Controller)

Bus 00h/

Dev14h/ Fun00

Output if GPO

(On SMBus

Controller)

Bus 00h/

Dev14h/ Fun00

Power

Domain

GPIO42/

ACZ_SDIN0

SMBus Extend Reg

00h[Bit1:0]

00/11: GPIO port

01: AC97 port

10: HD Audio port

Extend Reg 04h[Bit 0]

0: Output enable

1: Input (Tri-state)

Extend Reg

02h[Bit 0]

Extend Reg

06h[Bit 0]

S0

GPIO43/

ACZ_SDIN1

SMBus Extend Reg

00h[Bit3:2]

00/11: GPIO port

01: AC97 port

10: HD Audio port

Extend Reg 04h[Bit 1]

0: Output enable

1: Input (Tri-state)

Extend Reg

02h[Bit 1]

Extend Reg

06h[Bit 1]

S0

GPIO44/

ACZ_SDIN2

SMBus Extend Reg

00h[Bit5:4]

00/11: GPIO port

01: AC97 port

10: HD Audio port

Extend Reg 04h[Bit 2]

0: Output enable

1: Input (Tri-state)

Extend Reg

02h[Bit 2]

Extend Reg

06h[Bit 2]

S0

GPIO45/

AC_RST#

PM IO Reg59h[Bit 1:0]

00/01/10: AC97 port

11: GPIO

Extend Reg 05h[Bit 0]

0: Output enable

1: Input (Tri-state)

Extend Reg

03h[Bit 0]

Extend Reg

07h[Bit 0]

S0

GPIO46/

AZ_SDIN3

SMBus Extend Reg

00h[Bit7:6]

00/11: GPIO port

01: N/A

10: HD Audio port

Extend Reg 04h[Bit 3]

0: Output enable

1: Input (Tri-state)

Extend Reg

02h[Bit 3]

Extend Reg

06h[Bit 3]

S0

GPIO47/

SPI_CLK

SMBus RegA7h[Bit 6]

0: SPI_CLK

1: GPIO

Reg A6h[Bit 6]

0: Output

1: Input (Tri-state)

Reg A7h[Bit 2] Reg A6h[Bit 2] S0

GPIO48/

FANOUT1

PM IO Reg60h[Bit 2]

0: GPIO

1: FANOUT1

Reg A6h[Bit 7]

0: Output

1: Input (Tri-state)

Reg A7h[Bit 3] Reg A6h[Bit 3] S0

GPIO49/

FANOUT2

PM IO Reg60h[Bit 3]

0: GPIO

1: FANOUT2

Reg 50h[Bit 4]

0: Output

1: Input (Tri-state)

Reg 51h[Bit 0] Reg 50h[Bit 0] S0

GPIO50/

FANIN0

PM2 IO Reg31h[Bit 0]

0: GPIO

1: FANIN0

Reg 50h[Bit 5]

0: Output

1: Input (Tri-state)

Reg 51h[Bit 1] Reg 50h[Bit 1] S0

GPIO51/

FANIN1

PM2 IO Reg36h[Bit 0]

0: GPIO

1: FANIN1

Reg 50h[Bit 6]

0: Output

1: Input (Tri-state)

Reg 51h[Bit 2] Reg 50h[Bit 2] S0

GPIO52/

FANIN2

PM2 IO Reg3Bh[Bit 0]

0: GPIO

1: FANIN2

Reg 50h[Bit 7]

0: Output

1: Input (Tri-state)

Reg 51h[Bit 3] Reg 50h[Bit 3] S0