©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 137

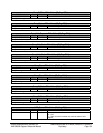

GpmPort - RW – 8 bits - [IO_Reg: C52h]

Field Name Bits Default Description

GpmPort register

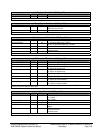

Isa_Misc - RW – 8 bits - [IO_Reg: C6Fh]

Field Name Bits Default Description

Reserved 5:0 00h

FlashRomEn 6 0b Flash program enable. This only applies if the chip is

strapped to have the ROM on the PCI bus . Set to 1 to enable

programming of the Flash ROM. During write cycles to the

system ROM space, ROMCS# is only asserted if this bit is

set 1.

Reserved 7 0b

Isa_Misc register: FlashRom Enable. This only applies if the chip is strapped to have the ROM on the secondary

PCI bus.

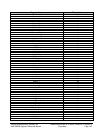

BIOSRAM_Index - RW – 8 bits - [IO_Reg: CD4h]

Field Name Bits Default Description

BiosRamIndex 7:0 00h BIOS RAM index register. This register selects one of the

256 bytes of BIOS RAM. Data in this RAM is preserved until

RSMRST# is asserted, or S5 power is lost.)

BiosRamIndex register

BIOSRAM_Data - RW – 8 bits - [IO_Reg: CD5h]

Field Name Bits Default Description

BiosRamData 7:0 00h Power management data register. This register provides the

read/write access to the indexed register.

BiosRamData register

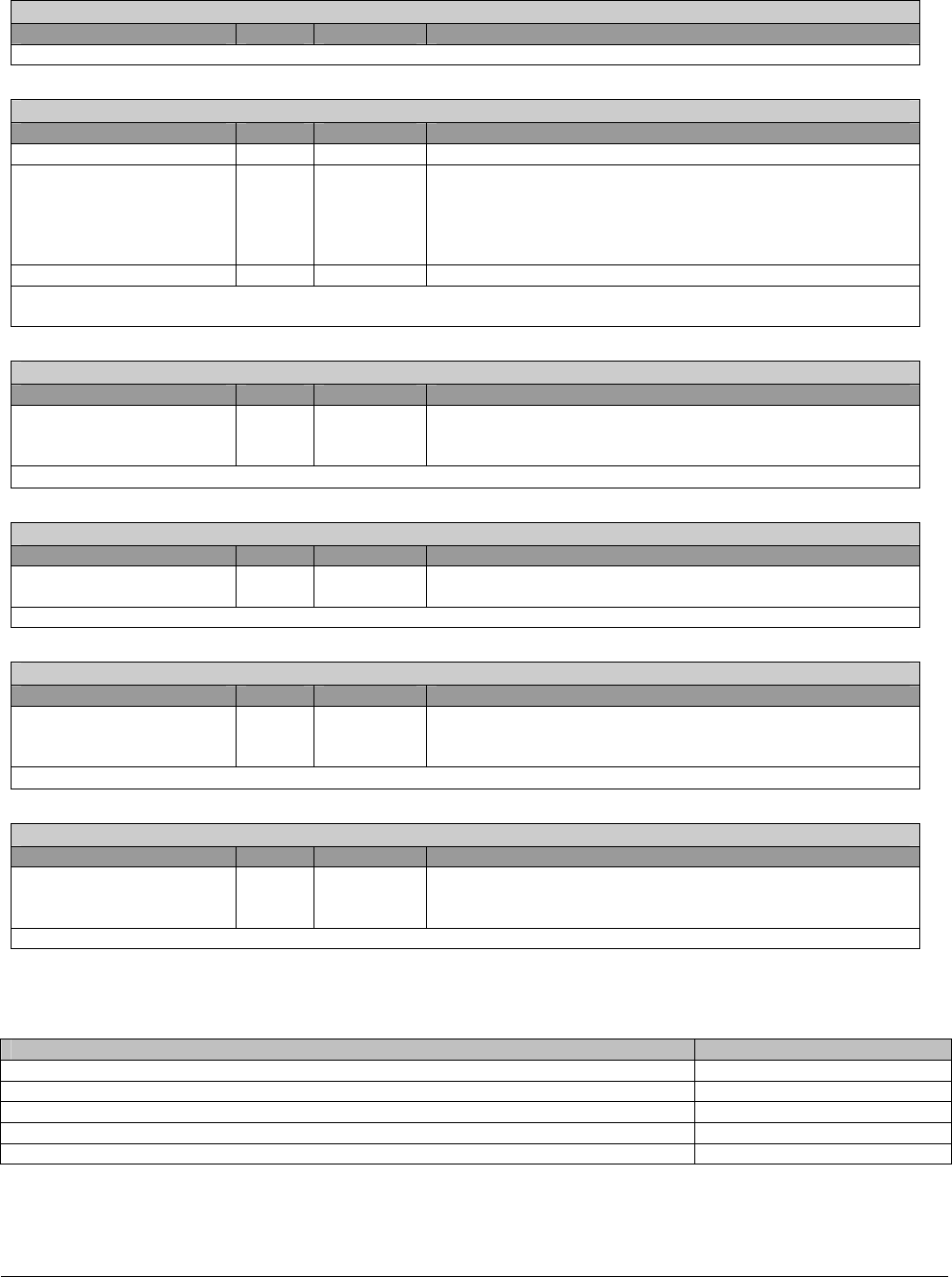

PM_Index - RW – 8 bits - [IO_Reg: CD6h]

Field Name Bits Default Description

PM_Index 7:0 00h Power management index register. This register selects one

of the Power Management registers. (See section 2.3.3.2 for

more information.)

PM_Index register

PM_Data - RW – 8 bits - [IO_Reg: CD7h]

Field Name Bits Default Description

PM_Data 7:0 00h Power management data register. This register provides the

read/write access to the indexed register. (See section

2.3.3.2 for more information.)

PM_Data register

2.3.3.1.2 Client Management Registers (Accessed through C50h and C51h)

Register Name Offset Address

IdRegister 00h

TempStatus 02h

TempInterrupt 03h

I2Ccontrol 12h

Index13 13h