©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 82

HCSP-PORTROUTE – R - 60 bits - [MEM_Reg : 0Ch]

Description

This optional field is valid only if Port Routing Rules field in the HCSPARAMS register is set to a one. This field is a

15-element nibble array (each 4 bits is one array element). Each array location corresponds one-to-one with a

physical port provided by the host controller.

2.2.3.3 Host Controller Operational Registers (EOR_Reg)

This block of registers is memory-mapped. The base offset, EHCI_EOR, is defined in CAPLENGTH register

(MEM_Reg: 00h, default value = 20h).

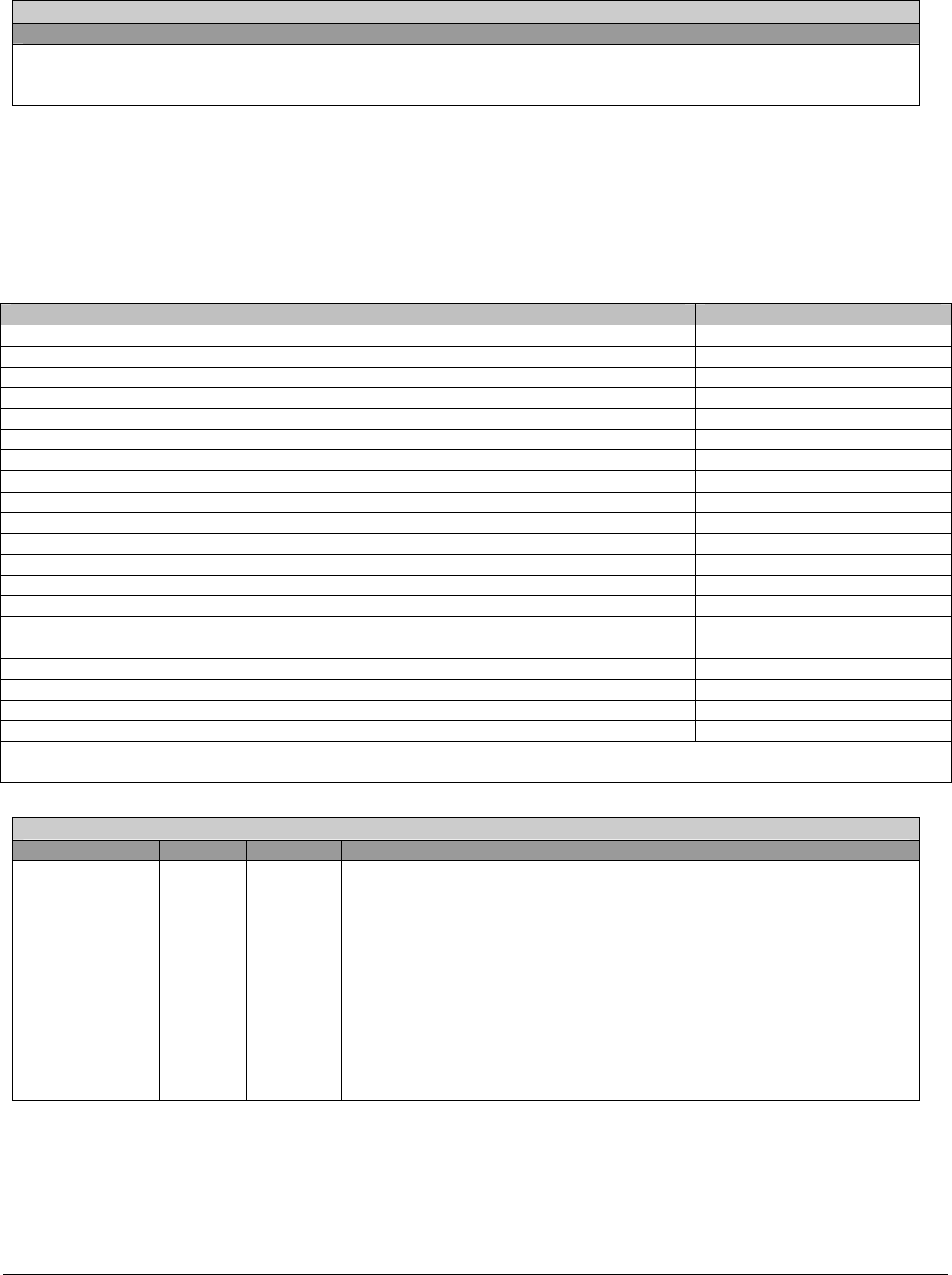

Registers Name Offset Address

USB Command – USBCMD EHCI_EOR + 00h

USB Satus – USBSTS EHCI_EOR + 04h

USB Interrupt Enable – USBINTR EHCI_EOR + 08h

USB Frame Index – FRINDEX EHCI_EOR + 0Ch

4G Segment Selector – CTRLDSSEGMENT EHCI_EOR + 10h

Frame List Base Address – PERIODICLISTBASE EHCI_EOR + 14h

Next Asynchronous List Address – ASYNCLISTADDR EHCI_EOR + 18h

Reserved EHCI_EOR + (1Ch~3Fh)

Configured Flag – CONFIGFLAG EHCI_EOR + 40h

Port Status/Control – PORTSC (1-N_PORTS) EHCI_EOR + (44h~68h)

Packet Buffer Threshold Values EHCI_EOR + 84h

USB PHY Status 0 EHCI_EOR + 88h

USB PHY Status 1 EHCI_EOR + 8Ch

USB PHY Status 2 EHCI_EOR + 90h

UTMI Control EHCI_EOR + 94h

Bist Control / Loopback Test EHCI_EOR + 98h

EOR MISC Control EHCI_EOR + 9Ch

USB Phy Calibration EHCI_EOR + A0h

EOR Debug Purpose EHCI_EOR + A8h

USB Debug Port 0E0h~0F0h (* Note)

The base offset of Debug Port registers is defined directly in DBUG_PRT Control register (EHCI_PCI_CFG xE4[28:16]),

regardless of the value in CAPLENGTH register (MEM_Reg: 00h) so range is equivalent to EHCI_EOR + (C0h~D0h).

USBCMD – RW - 32 bits - [EOR_Reg : EHCI_EOR + 00h]

Field Name Bits Default Description

Run/Stop (RS)

0 0b 1=Run, 0=Stop.

When set to a 1, the Host Controller proceeds with execution of the

schedule. The Host Controller continues execution as long as this bit is

set to a 1. When this bit is set to 0, the Host Controller completes the

current and any actively pipelined transactions on the USB and then

halts. The Host Controller must halt within 16 micro-frames after

software clears the Run bit. The HC Halted bit in the status register

indicates when the Host Controller has finished its pending pipelined

transactions and has entered the stopped state. Software must not write

a one to this field unless the host controller is in the Halted state (i.e.

HCHalted in the USBSTS register is a one). Doing so will yield

undefined results.