©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 158

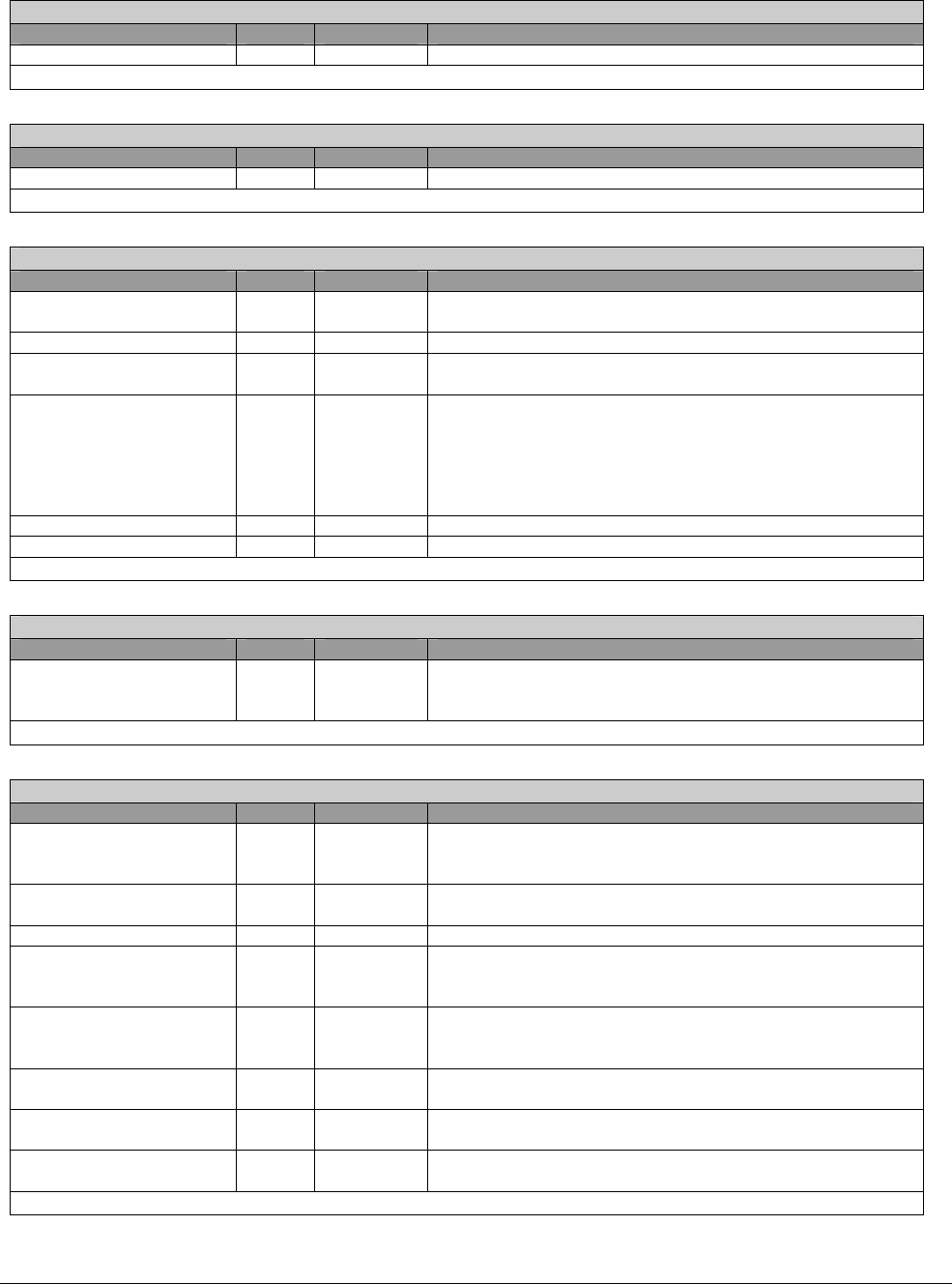

Reserved – 8 bits - [PM_Reg: 57h]

Field Name Bits Default Description

Reserved 7:0 00h

Reserved

Reserved – 8 bits - [PM_Reg: 58h]

Field Name Bits Default Description

Reserved 7:0 00h

Reserved

MiscOption - RW – 8 bits - [PM_Reg: 59h]

Field Name Bits Default Description

MaskAc97[1:0] 1:0 00b Setting the bit will mask out the ac97 PCI configuration space

(function 5, 6)

SataClkSelect 2 0b 0-external clock, 1-shared with PCIE 100MHz clock

AzEnable 3 1b 1 – Enable HD AUDIO module

0 – Disable HD AUDIO module

AzSnoopEnable 4 0b When set, HD AUDIO data transfer will not cause the

BM_STS bit to be set and to wake up the CPU from C3 state.

This is used when previous version of SB did not have C

state pop-up/down function. With the new pop-up/down

function in SB600, this function is not necessary and should

not be enabled if the C-state pop-up/down is enabled.

Gpio5ShutdownEn 5 0b Shutdown system if seeing a negative edge on Gpio5

Reserved 7:6 00b

MiscOption register

SmiSciSts0 - RW – 8 bits - [PM_Reg: 5Ah]

Field Name Bits Default Description

GeventStatus 7:0 00h These bits indicate the SMI# status of the eight general

purpose event signals if they are configured to generate SMI#

followed by SCI

SmiSciSts0 register

SmiSciSts1 - RW – 8 bits - [PM_Reg: 5Bh]

Field Name Bits Default Description

LEventStatus 0 0b This bit indicates the SMI# status of the legacy power

management logic if it is configured to generate SMI#

followed by SCI

TwarnStatus 1 0b This bit indicates the SMI# status of the Temperature Caution

input if it is configured to generate SMI# followed by SCI

Reserved 2 0b

USBStatus 3 0b This bit indicates the SMI# status of the PME# from the

internal USB controller if it is configured to generate SMI#

followed by SCI

AC97Status 4 0b This bit indicates SMI# status of the PME# from the internal

ac97 controller if it is configured to generate SMI# followed by

SCI

OtherThermStatus 5 0b This bit indicates the SMI# status of OtherTherm from NB,

fan, etc. if it is configured to generate SMI# followed by SCI

GPM9Status 6 0b This bit indicates the SMI# status of GPM[9] if it is configured

to generate SMI# followed by SCI

PCIeHotPlugStatus 7 0b This bit indicates the SMI# status of PCIeHotPlug if it is

configured to generate SMI# followed by SCI

SmiSciSts1 register