©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual Proprietary Page 274

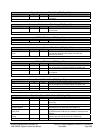

Dual Address Cycle Enable and PCIB_CLK_Stop Override - RW - 16 bits - [PCI_Reg: 50h]

Field Name Bits Default Description

ClkrunOvrridePCICLK 6 0b When set, overrides the CLKRUN# and 33MHz PCICLK

continues to run.

ClkrunOvrridePCICLK1 7 0b When set, overrides the CLKRUN# and 33MHz PCICLK1

continues to run.

ClkrunOvrridePCICLK2 8 0b When set, overrides the CLKRUN# and 33MHz PCICLK2

continues to run.

ClkrunOvrridePCICLK3 9 0b When set, overrides the CLKRUN# and 33MHz PCICLK3

continues to run.

ClkrunOvrridePCICLK4 10 0b When set, overrides the CLKRUN# and 33MHz PCICLK4

continues to run.

ClkrunOvrrideLPCCLK 11 0b When set, overrides the CLKRUN# and LPCCLK continues

to run.

ClkrunOvrrideLPCCLK1 12 0b When set, overrides the CLKRUN# and LPCCLK1 continues

to run

ClkrunOvrridePCICLK7 13 0b When set, overrides the CLKRUN# and 33MHz PCICLK7

continues to run.

ClkrunOvrridePCICLK8 14 0b When set, overrides the CLKRUN# and 33MHz PCICLK8

continues to run.

ClkrunOvrridePCICLK9 15 0b When set, overrides the CLKRUN# and 33MHz PCICLK9

continues to run.

Dual Address Cycle Enable and PCIB_CLK_Stop Override

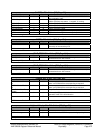

MSI Mapping Capability – R - 32 bits - [PCI_Reg: 54h]

Field Name Bits Default Description

MSI Cap ID 7:0 08h MSI Capability ID

MSI Cap Pointer 15:8 00h MSI Capabilities Pointer

MSI Cap Enable 16 1b MSI Capabilities Enable

MSI Fixed 17 1b MSI Fixed

MSI Reserved 26:18 000h Reserved

MSI CapType 31:27 15h MSI Capability Type

MSI Mapping Capability

Signature Register for Microsoft Rework for Subtractive Decode

- R - 32 bits - [PCI_Reg: 58h]

Field Name Bits Default Description

Signature Register for

Microsoft Rework

for Subtractive Decode

31:0 00000000

h

When Microsoft Rework for Subtractive Decode is done,

this register will contain the signature value

Signature Register for Microsoft Rework for Subtractive Decode

Prefetch Timeout Limit - 16 bits - [PCI_Reg: 5Ch]

Field Name Bits Default Description

Prefetch Timeout Limit 15:0 0085h When deep prefetch is enabled (reg0x64[7]=1), this timer

determines when to flush the staled data in the buffer. Each

count is 30ns

SPCI IDSEL MaskB - 16 bits - [PCI_Reg: 5Eh]

Field Name Bits Default Description

PCI IDSEL MaskB 15:0 FFFFh Each bit represents the masking the specific device on the

PCI bus. The purpose of this register is to hide the device

from OS

0—The corresponding IDSEL bit is masked

1—The corresponding IDSEL bit is not masked.