©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 156

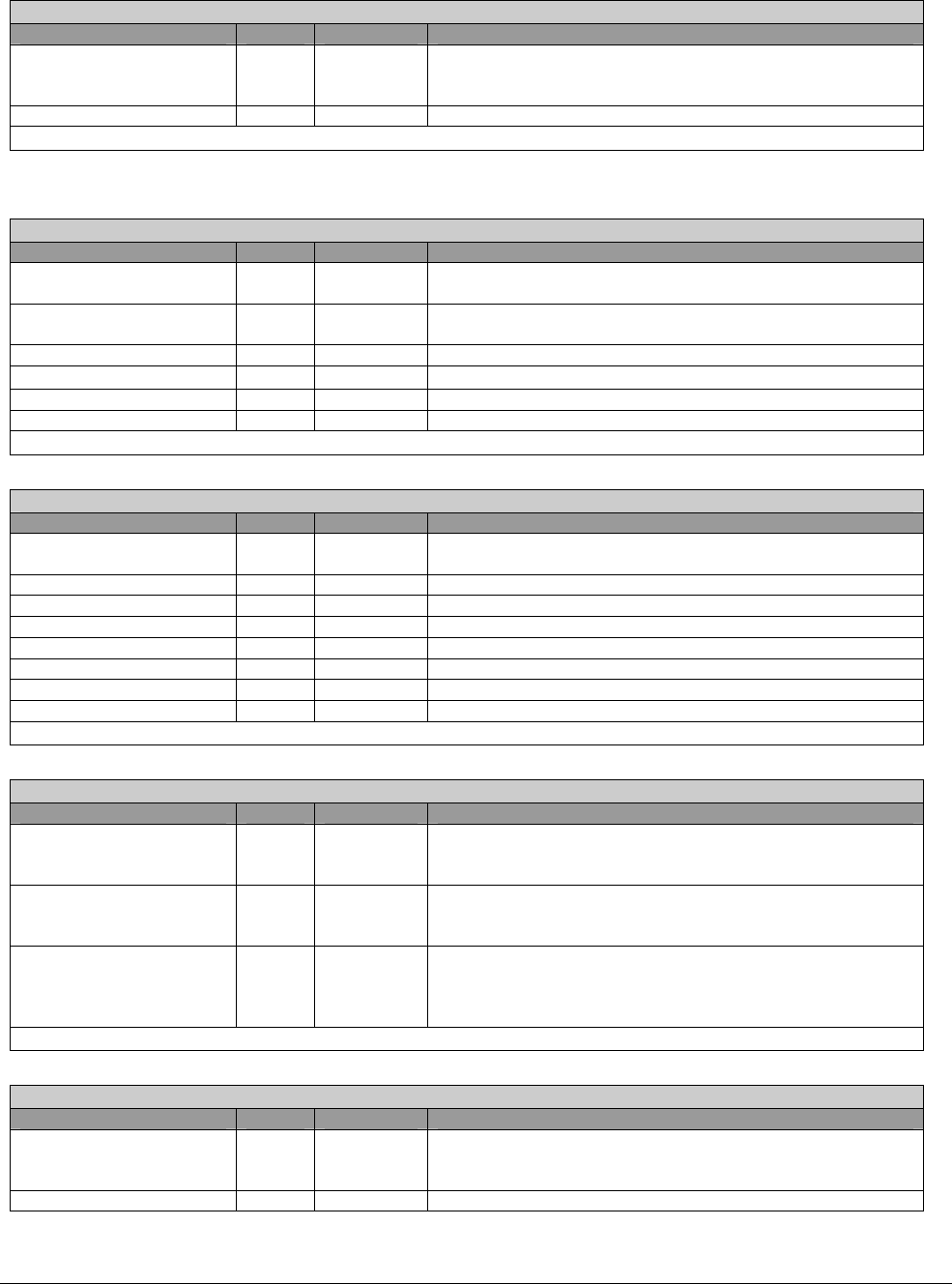

AD23_Pull_UpB - RW – 8 bits - [PM_Reg: 41h]

Field Name Bits Default Description

AD23_Pull_UpB 0 0b This bit controls integrated pull-up for AD[23].

0: Enable

1: Disable

Reserved 7:1 0000_000b

AD23_Pull_UpB register.

MiscPmControl - RW – 8 bits - [PM_Reg: 42h]

Field Name Bits Default Description

CPU_IO_PullDownDrvStr

ength

0 0b When set, the integrated pull-down drive strength of all CPU

IOs are increased by 50%

DisableBootFailCpuRst 1 0b This bit can be used to disable the boot fail timer to generate

CPURST#/LDTRST#

C2ToC3Enable 2 0b When set, SB will treat C2 as C3 under K8 mode

RstCpuPGEnable

3 0b If this bit is set to 1, SB toggles CPUPG on every reset

Reserved 6:4 000b

SSEnable 7 0b Enables the spread spectrum PLL

MiscPmControl

PM_Enable - RW – 8 bits - [PM_Reg: 50h]

Field Name Bits Default Description

C3_DPRSLP_EN 0 0b When set, reading LVL3 register will cause “deeper” sleep for

Intel® mobile P4. This is equivalent to LVL4 read.

CPU_STP_EN_S2 1 0b When set, CPU_STP# will be asserted in S2

CPU_STP_EN_S3 2 0b When set, CPU_STP# will be asserted in S3

CPU_STP_EN_S5 3 0b When set, CPU_STP# will be asserted in S5

AGP_STP_EN 4 0b When set, AGP_STP# message will be enabled.

PCI_STP_EN_S2 5 0b When set, PCI_STP# will be asserted in S2

PCI_STP_EN_S3 6 0b When set, PCI_STP# will be asserted in S3

PCI_STP_EN_S5 7 0b When set, PCI_STP# will be asserted in S5

PM_Enable register

TPRESET1 - RW – 8 bits - [PM_Reg: 51h]

Field Name Bits Default Description

TPRESET1 5:0 00h Timing parameter used for C states in P4 system. This

register defines the wakeup latency in 8µs increment with 8us

uncertainty.

BmStsRdMask

(available after A13)

6 0b Setting this bit to 1 will keep BM_STS read as 0, unless the

BM_STS is caused by USB OHCI and UsbOhciBmStsRdEn

is set to 1.

StpClkHoldSel

(available after A12)

7 0b Use this bit to select STPCLK# hold time with respect to

SLP#

0: 200ns

1: 3.9us

TPRESET1 register

TPRESET2 - RW – 8 bits - [PM_Reg: 52h]

Field Name Bits Default Description

TPRESET2 5:0 00h Timing parameter used for S* -> S0 state transitions. This

register determines the CPU_STP# deassertion delay in 8µs

increment with 8us uncertainty.

Reserved 6 0b