©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 36

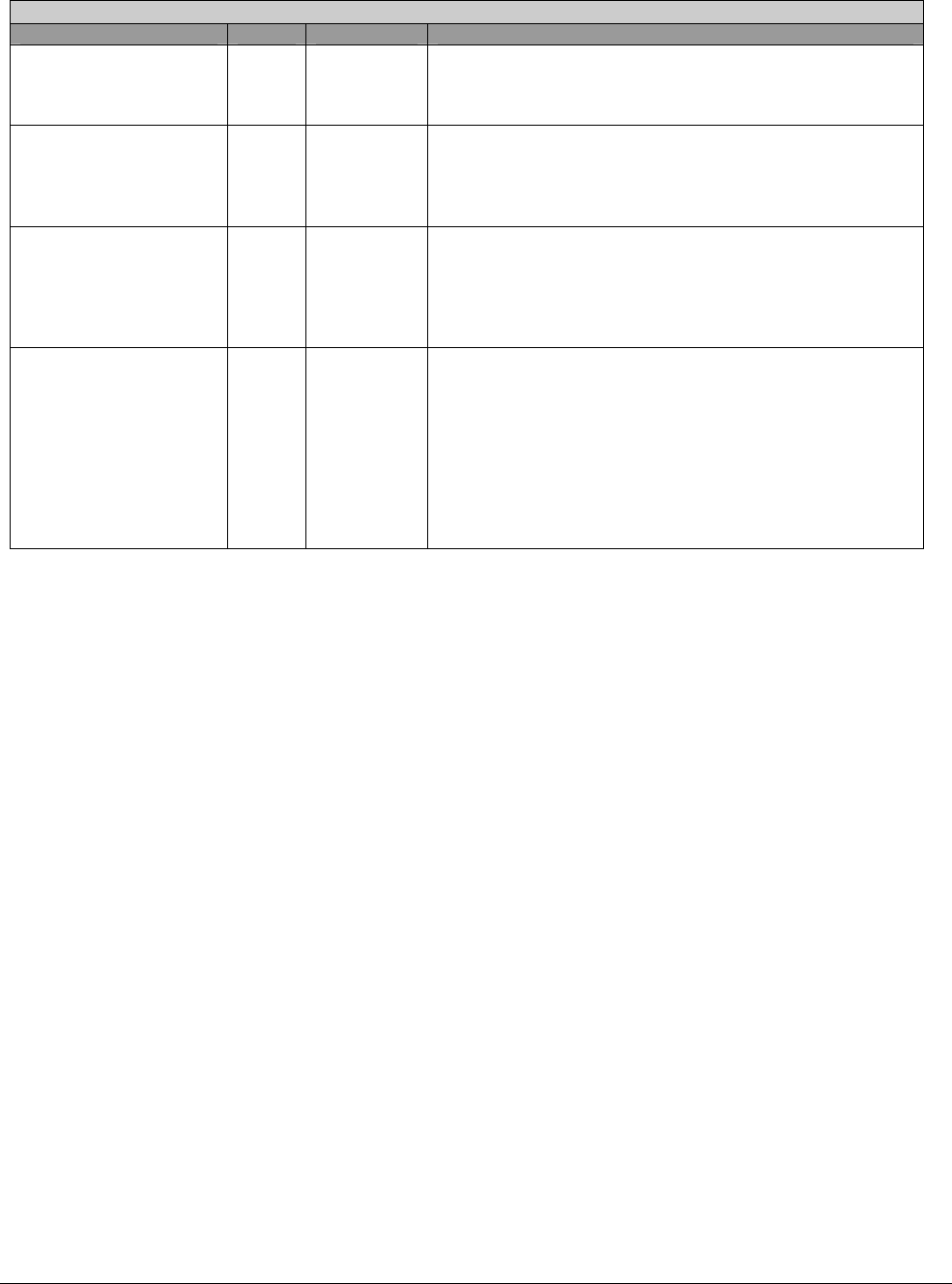

Port-N Command and Status - R - 32 bits [Mem_reg: ABAR + port offset + 18h]

Field Name Bits Default Description

Device is ATAPI (ATAPI) 24 0b RW

When set to ‘1’, the connected device is an ATAPI device.

This bit is used by the HBA to control whether or not to

generate the desktop LED when commands are active.

Drive LED on ATAPI

Enable (DLAE)

25 0b RW

When set to ‘1’, the HBA shall drive the LED pin active for

commands regardless of the state of P0CMD.ATAPI. When

cleared, the HBA shall only drive the LED pin active for

commands if P0CMD.ATAPI set to ‘0’.

Aggressive Link Power

Management Enable

(ALPE)

26 0b RW

When set to ‘1’, the HBA shall aggressively enter a lower link

power state (Partial or Slumber) based upon the setting of the

ASP bit. Software shall only set this bit to ‘1’ if CAP.SALP is

set to ‘1’; if CAP.SALP is cleared to ‘0’ software shall treat

this bit as reserved.

Aggressive Slumber /

Partial (ASP)

27 0b RW

When set to ‘1’, and ALPE is set, the HBA shall aggressively

enter the Slumber state when it clears the PxCI register and

the PxSACT register is cleared or when it clears the PxSACT

register and PxCI is cleared. When cleared, and ALPE is set,

the HBA shall aggressively enter the Partial state when it

clears the PxCI register and the PxSACT register is cleared

or when it clears the PxSACT register and PxCI is cleared. If

CAP.SALP is cleared to ‘0’ software shall treat this bit as

reserved.