©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual Proprietary Page 276

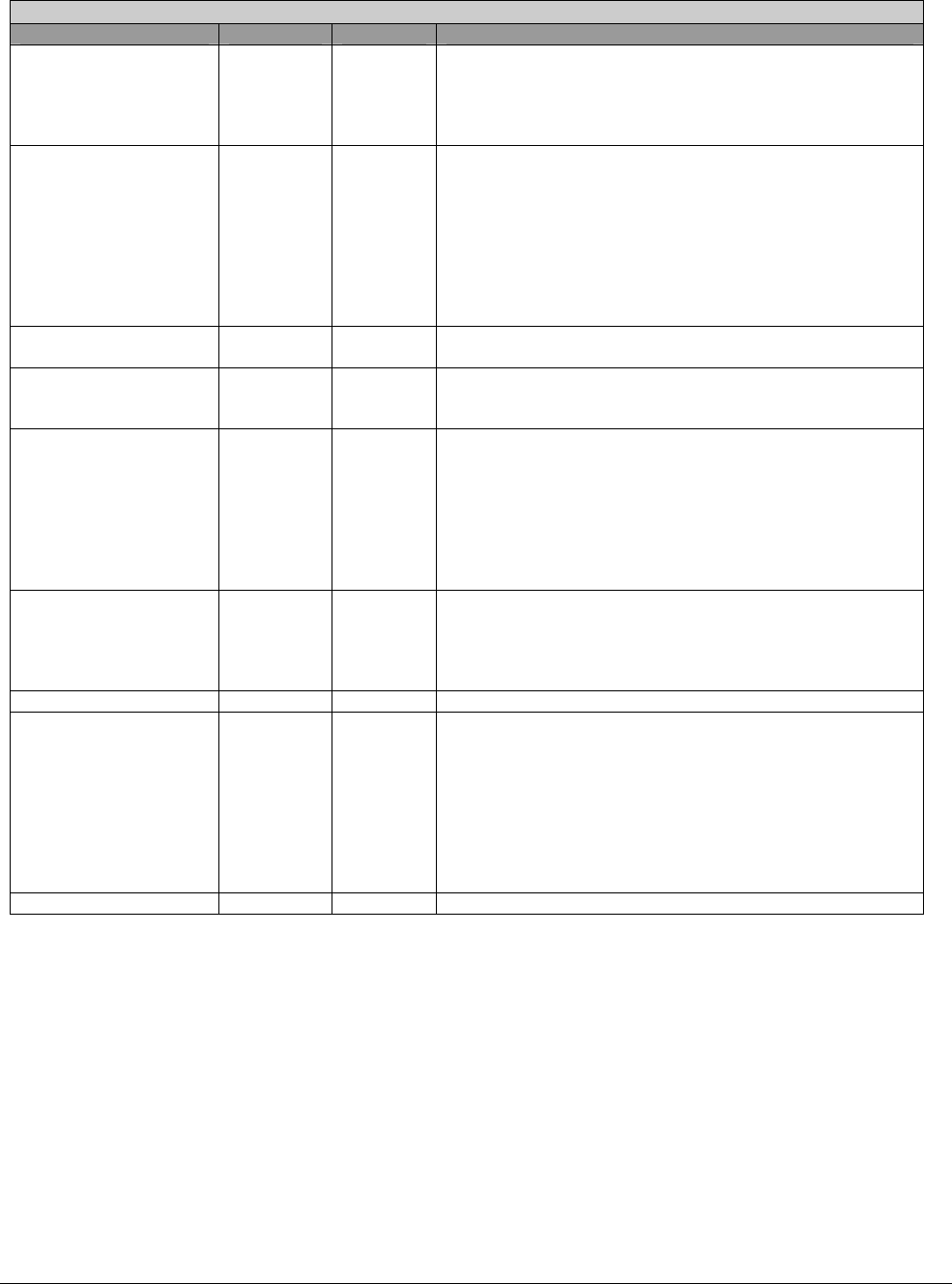

Misc Control Register - 32 bits - [PCI_Reg: 64h]

Field Name Bits Default Description

Prefetch Enable For

Upstream Read Line

and Read Multiple

7 1h 0: Prefetch is disabled for upstream memory read line and

memory read multiple.

1: Prefetch is enabled for upstream memory read line and

memory read multiple.

Also refer to reg0x40[4] and reg0x64[21].

PCI5 Enable 8 0h Setting this bit will enable PCIGNT5#/PCIREQ5# and

PCICLK7.

Note: These three pins are all using this single configuration

bit to enable them into PCI functionality. Care should

therefore be taken to ensure that they are used as intended.

Since PCICLK7 is not programmed as PCICLK by default,

the BIOS needs exercise a certain sequence in order to

make the clock valid. For more information consult the AMD

SB600 Register Programming Requirements guide.

Arbiter 2 Enable 9 0h Enables the use of the new PCI bus arbiter to replace the

old arbiter.

Hold Current Grant 10 0h When set, PCIGNT# will not be deasserted until the

requesting agent deasserts its PCIREQ#. This only applies

to the new PCI bus arbiter

Single Cycle Prefetch

Control

11 1h If a prefetch read cycle comes from SPCI bus, prefetching

may not be necessary if the cycle is single data phase. PCIB

can optionally treat the single cycle as non-prefetch and only

asks for one dword from AB.

1—Turn on the ability to treat single data phase cycle as

non-prefetch cycle.

0—Turn off the ability to treat single data phase cycle as

non-prefetch cycle.

Fast Grant Deassert En 12 0b This control bit applies only to the old (default) PCI arbiter.

Normally PCIGNT# is deasserted two clocks after PCIREQ#

deasserts. With this bit set, PCIGNT# will deassert 1 clock

after PCIREQ# deasserts. Recommendation is to have this

bit set.

Reserved 20:13 0h

Prefetch Disable for

Upstream Mem Read

21 0h In A11~A13: Reserved.

In A21 and later versions:

0: Prefetch is enabled for upstream normal memory read

(other than read line or read multiple). However, if

reg0x64[7]=0, then this prefetch is still disabled.

1: Prefetch is disabled for upstream normal memory read

(other than read line or read multiple).

Also refer to reg0x40[4] and reg0x64[7].

Reserved 31:22 0h