©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 136

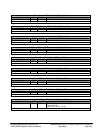

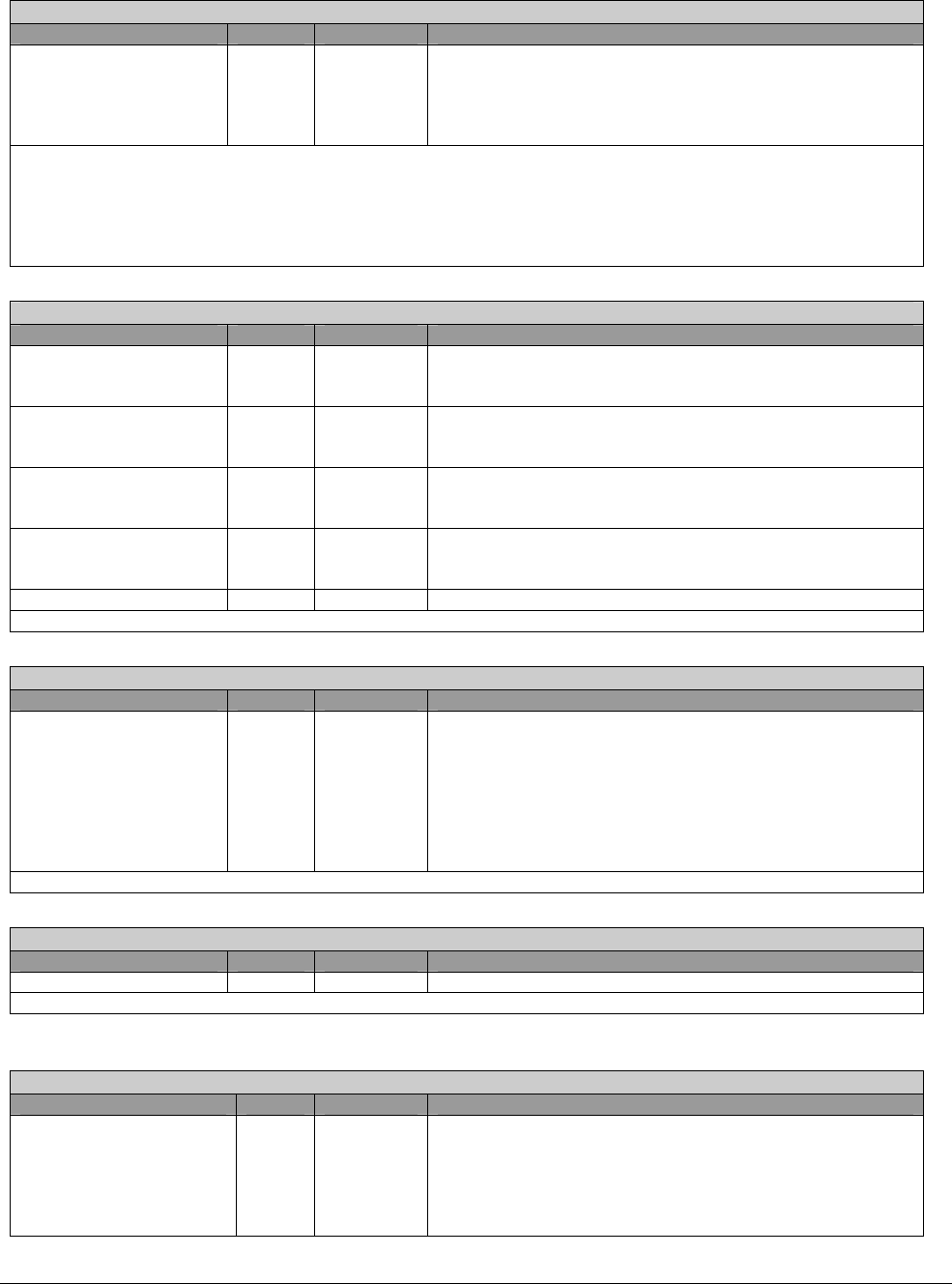

Pci_Intr_Data - RW – 8 bits - [IO_Reg: C01h]

Field Name Bits Default Description

Pci_Intr_Data 7:0 00h PCI redirection register; map PCI interrupt addressed by

Pci_Intr_Index to a PIC IRQ

[7:4] – Not used

Straight encoding of [3:0] to : IRQ0 thru IRQ15

Note: Do not map to IRQ 0, 2, 8, 13 – they are reserved

Pci_Intr_Data register

Note: If IOXAPIC is enabled, software must make sure interrupts are not re-routed; i.e., they should all be set to 0.

When IOXAPIC is enabled, IRQ[15:0] are routed directly to INT[15:0]. INTH#, INTG#, INTF#, INTE#, INTD#, INTC#,

INTB#, and INTA# are routed to INTIN[23:16], SMBus interrupt is routed to INTIN[20], SCI# is routed to INTIN[9],

and the High Precision Event Timer (also called the Multimedia Timer) can be routed to either INTIN[22] or

INTIN[23].

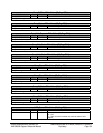

Pci_Error - RW – 8 bits - [IO_Reg: C14h]

Field Name Bits Default Description

Serr_Nmi_Status 0 - Set to 1 when NMI generation is enabled and SERR# has

been asserted due to a PCI error. Cleared by writing a one to

port 61h, bit 2. [Read-only]

Perr_Nmi_Status 1 - Set to 1 when NMI generation is enabled and PERR# has

been asserted due to a PCI data parity error. Cleared by

writing a one to port 61h, bit 2. [Read-only]

Serr_Nmi 2 1b Enable NMI generation from SERR#

0 – Enable

1 – Disable

Perr_Nmi 3 1b Enable NMI generation from PERR#

0 – Enable

1 – Disable

Reserved 7:4 0h

Pci_Error register

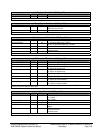

CMIndex - RW – 8 bits - [IO_Reg: C50h]

Field Name Bits Default Description

CMIndex 7:0 00h Index register to client management register block

00h – IdRegister

02h – TempStatus

03h – TempInterrupt

12h – SmBus control (control to Gpoc[3:0] pins

thru Bit Bang)

13h - Misccontrol

others – super IO – not used

CMIndex register

CMData - RW – 8 bits - [IO_Reg: C51h]

Field Name Bits Default Description

CMData 7:0 00h Data register to client management register block

CMData register

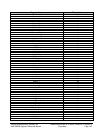

GpmPort - RW – 8 bits - [IO_Reg: C52h]

Field Name Bits Default Description

Gpm 7:0 -- If CMIndex.13h[7:6] == 00, then this is the read port for

GPM[7:0].

If CMIndex.13h[7:6]= 01, then this is the output enable for

GPM[7:0], 0=enable, 1=tristate

If CMIndex.13h[7:6]=10, then this is the output state control

(providing enable is turned on)