©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 130

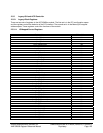

Tmr1CntrlWord - RW – 8 bits - [IO_Reg: 43h]

Field Name Bits Default Description

CntDownSelect 0 0b 0 – Binary countdown

1 – BCD countdown

ModeSelect 3:1 000b 000 – Asserts OUT signal at end of count

001 – Hardware re-triggerable one-shot

010 – Rate generator

011 – Square wave output

100 – Software triggered strobe

101 – Hardware triggered strobe

110 – 111 – not used

CmmandSelect 5:4 00b 00 – Counter latch command

01 – Read/write least significant byte

10 – Read/write most significant byte

11 – Read/write least, and then most significant byte

CounterSelect 7:6 00b 00 - Select counter 0

01 - Select counter 1

10 - Select counter 2

11 – Read back command

Tmr1CntrlWord register: This is the control word to access the 8254 timer 1. It is used to select which counter will

be accessed and how it will be accessed. This register specifies the counter, the operating mode, the order and

size of the count value, and whether it counts down in a 16 bit or BCD format.

If a counter is programmed to read or write two-byte counts, the following precaution applies: A program must not

transfer control between writing the first and second byte to another routine which also writes into that same

counter; otherwise, the counter will be loaded with an incorrect value. The count must always be completely loaded

with both bytes.

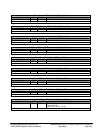

Nmi_Status - RW – 8 bits - [IO_Reg: 61h]

Field Name Bits Default Description

SpkrEnable 0 0b 0 - Disable counter 2

1 - Enable counter 2

SpkrTmrEnable 1 0b 0 - Speaker timer off

1 - Speaker timer on

Parity_Nmi_En 2 1b 0 - Enable Parity Error to NMI generation (from SERR# or

PERR#)

1 - Disable Parity Error to NMI generation and clear bit 7

Iochk_Nmi_En 3 1b 0 - Enable IoChk to NMI generation

1 - Disable IoChk to NMI generation

RefClk 4 - The output of the counter 1 (8254). (Read-only)

SpkrClk 5 - The output of the counter 2. [Read-only]

IoChk_Nmi 6 - NMI is triggered by serial IOCHK. [Read-only]

ParErr_Nmi 7 - NMI is caused by parity error (either PERR# or SERR#).

[Read-only]

Nmi_Status register: Independent read and write registers will be accessed at this port. When writing to port 61H,

bits[3:0] allow software to enable/disable parity error NMI's and control the speaker timer. When reading port 61H,

status on parity errors, speaker count, speaker control and refresh cycles is returned.

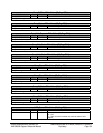

Nmi_Enable - RW – 8 bits - [IO_Reg: 70h]

Field Name Bits Default Description

RTC Address Port 6:0 00h This is used with either internal RTC or external RTC

NmiEnable 7 0b 0 - NMI enable

1 - NMI disable [Write-only]

Nmi_Enable register

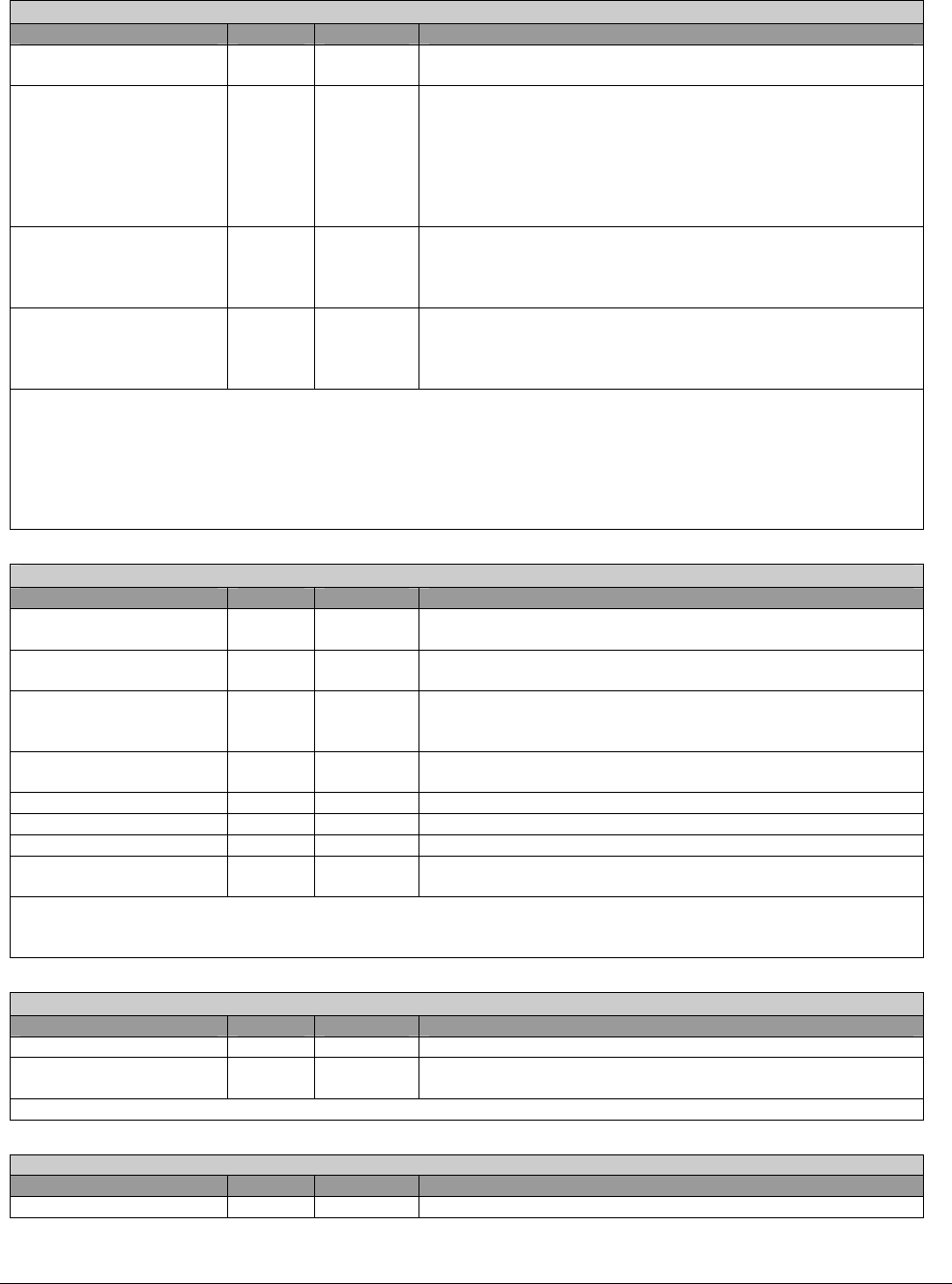

RtcDataPort - RW – 8 bits - [IO_Reg: 71h]

Field Name Bits Default Description

RTC Data Port 7:0 00h This is used with either internal RTC or external RTC