©2008 Advanced Micro Devices, Inc.

LPC ISA Bridge (Device 20, Function 3)

AMD SB600 Register Reference Manual Proprietary Page 251

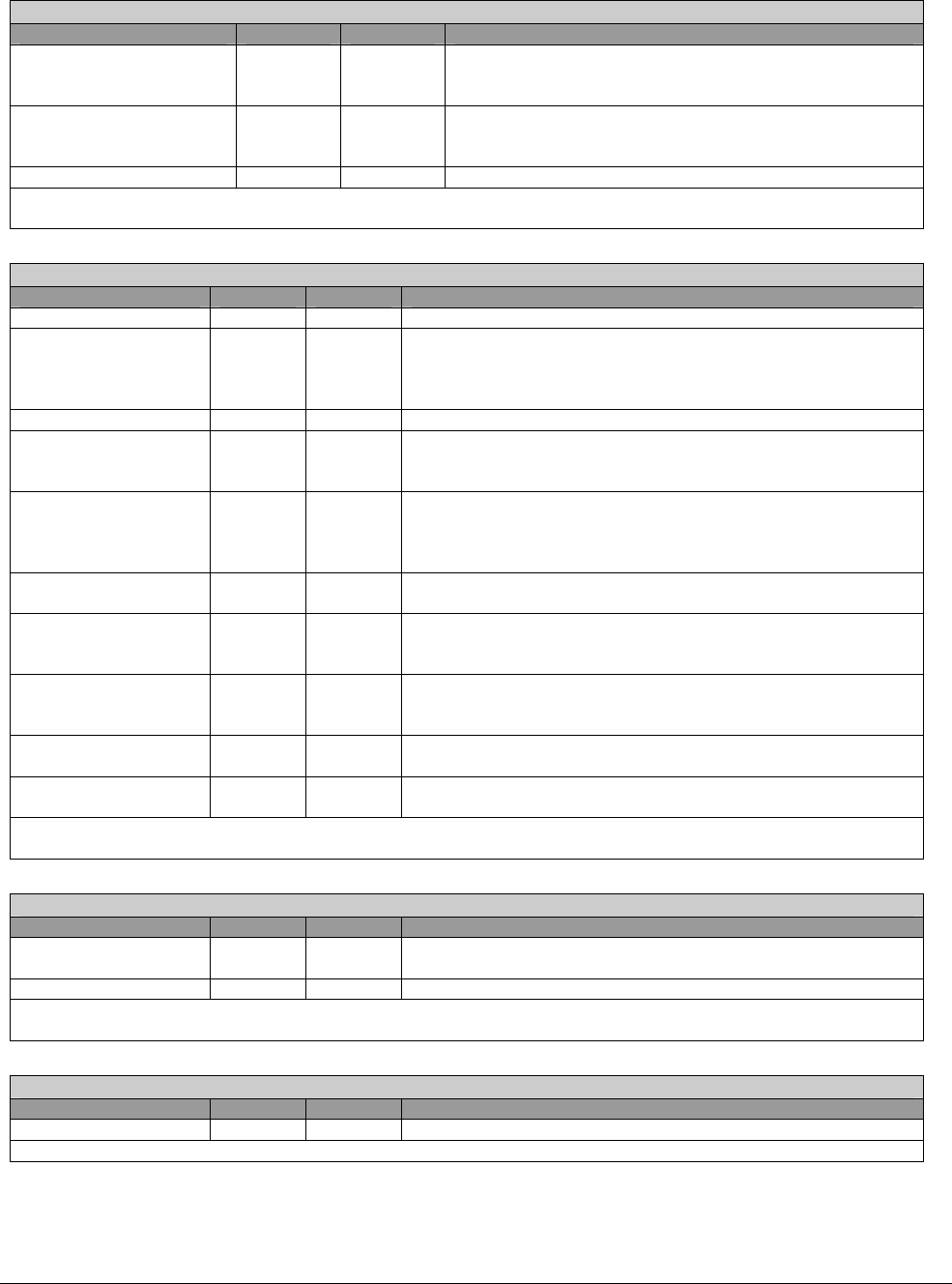

CMD- RW - 16 bits - [PCI_Reg: 04h]

Field Name Bits Default Description

SERR# Enable 8 0b SERR# enable - If set to 1, the LPC bridge asserts SERR#

when it detects as address parity error. SERR# is not

asserted if this bit is 0.

Fast Back-tp-Back Enable 9 0b Hardcoded to 0 to indicate that Fast Back-to-back is

disabled. The LPC bridge only acts as a master to a single

device, so this functionality is not needed.

Reserved 15:10 00h

Command Register: The PCI specification defines this register to control a PCI device’s ability to generate and

respond to PCI cycles.

STATUS- RW - 16 bits - [PCI_Reg: 06h]

Field Name Bits Default Description

Reserved 3:0 0h

Capabilities List 4 0b This bit is read only. When reg0x78[1] is 1, this bit reads 1; when

reg0x78[1] is 0, this bit reads 0. This is to satisfy K8

requirement. For P4 system, 0x78[1] should be set to 0 to mask

off this bit.

Reserved 7:5 0h

Master Data Parity

Error

8 0h Data Parity reported – Set to 1 if the LPC bridge detects PERR#

asserted while acting as PCI master (whether PERR# was driven

by the LPC bridge or not.)

Device Select Timing 10:9 1h DEVSEL# timing – Read only bits indicating DEVSEL# timing

when performing a positive decode.

Since DEVSEL# is asserted to meet the medium timing, these

bits are encoded as 01b.

Signaled Target Abort 11 0b Signaled Target Abort – This bit is set to 1 when the LPC bridge

signals Target Abort.

Received Target Abort 12 0b Received Target Abort – This bit is set to 1 when the LPC bridge

-generated PCI cycle is aborted by a PCI target. Cleared by

writing a 1 to it.

Received Master Abort 13 0b Received Master Abort Status. Set to 1 when the LPC bridge

acts as a PCI master and aborts a PCI bus cycle. Cleared by

writing a 1 to this bit.

Signaled System Error 14 0b SERR# status. This bit is set to 1, when the LPC bridge detects

a system error.

Detected Parity Error 15 0b Detected Parity Error. This bit is set to 1 when the LPC bridge

detects a parity error.

Status Register: The PCI specification defines this register to record status information for PCI related events.

Writing 0 to a bit has no effect; writing 1 to a bit will clear it to 0.

Revision ID/Class Code - R - 8 bits - [PCI_Reg: 08h]

Field Name Bits Default Description

Revision ID

7:0 00h These bits are hardwired to 00h to indicate the revision level of

the chip design

Class Code 31:8 060100h Class Code.

Revision ID/Class Code Register: This read only register contains the device’s revision information and generic

function. Since SB600 is an ISA bridge, its assigned class code is 060100h.

Cache Line Size - R - 8 bits - [PCI_Reg: 0Ch]

Field Name Bits Default Description

Cache Line Size 7:0 00h Cache Line Size.

Cache Line Size Register: This register specifies the system cache line size. This register is not implemented.