©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 176

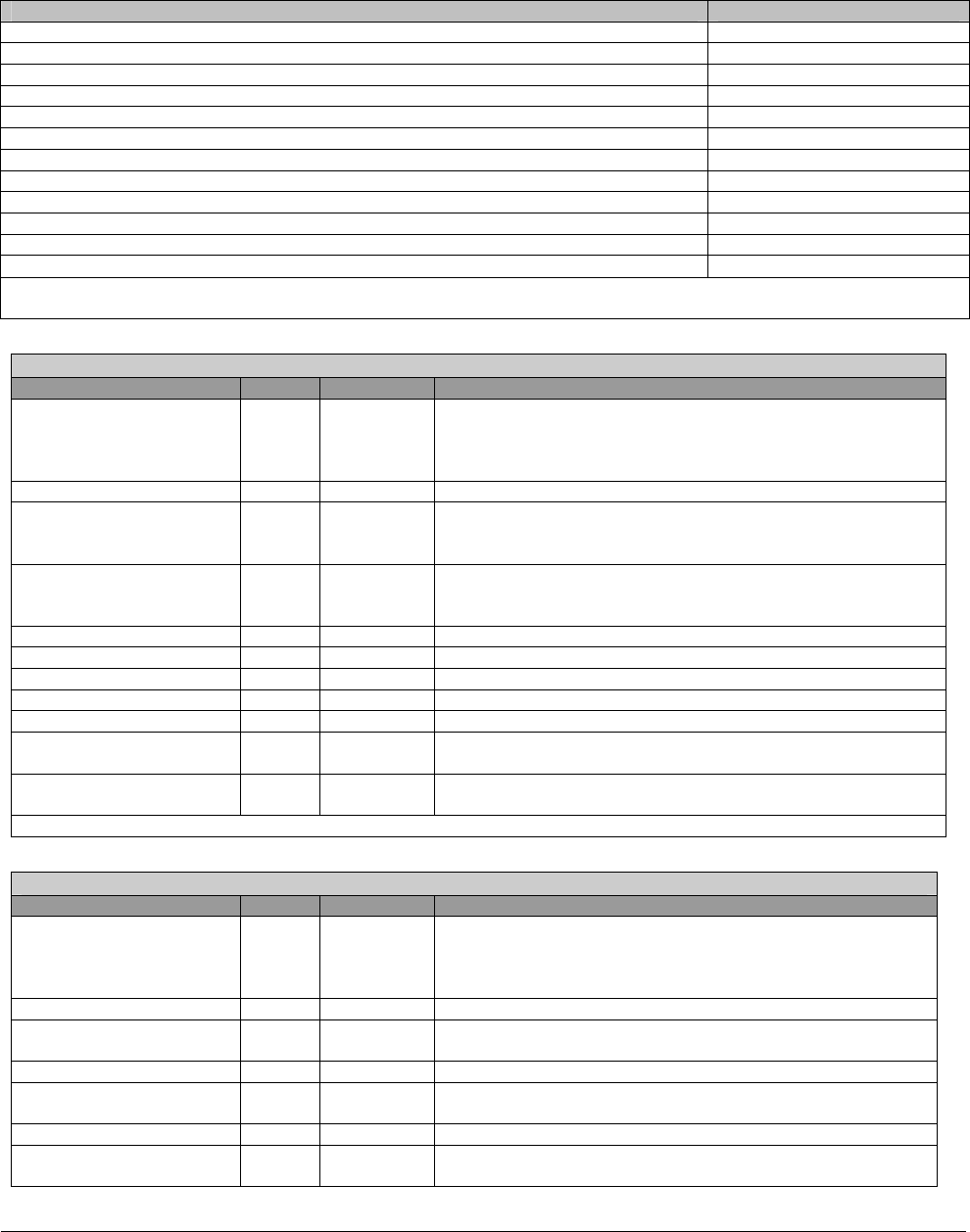

2.3.3.3 ACPI Registers

Register Name Offset Address*

Pm1Status 00h

Pm1Enable 02h

PmControl 00h

PmaControl 00h

TmrValue/ETmrValue 00h

CLKVALUE 00h

PLvl2 04h

PLvl3 05h

PLvl4 06h

AcpiSsCnt 00h

EVENT_STATUS 00h

EVENT_ENABLE 04h

* Note: The offset addresses listed here for the ACPI registers belong to different apertures/decodes. Check the register

descriptions for details.

Pm1Status - RW - 16 bits - [AcpiPmEvtBlk:00h]

Field Name Bits Default Description

TmrStatus 0 0b Timer carry status bit. This bit gets set anytime the 23

rd

/31

st

bit of 24/32 bit counter changes (whenever the MSB changes

from low to high or high to low. While TmrEn and TmrStatus

are set, an interrupt event is raised). [Read-only]

Reserved 3:1 000b

BmStatus 4 0b Bus master status bit. This bit is set any time a system bus

master requests the system bus, and can only be cleared by

writing an one to this bit position.

GblStatus 5 0b This bit is set when an SCI is generated due to the BIOS

wanting the attention of the SCI handler. This is set by writing

1 to PM_Reg: 0Eh bit [1].

Reserved 7:6 00b

PwrBtnStatus 8 0b Power button status bit

Reserved 9 0b

RtcStatus 10 0b This bit is set when RTC generates an alarm.

Reserved 13:11 000b

PciExpWakeStatus 14 0b This bit is set by hardware to indicate that the system woke

due to a PCI Express wakeup event.

WakeStatus 15 0b This bit is set when the system is in the sleep state and a

wake-up event occurs.

This register is located at the base address defined by AcpiPmEvtBlk.

Pm1Enable - RW - 16 bits - [AcpiPmEvtBlk:02h]

Field Name Bits Default Description

TmrEn 0 0b This is the timer carry interrupt enable bit. When this bit is

set then an SCI event is generated anytime the TmrStatus is

set. When this bit is reset then no interrupt is generated

when the TmrStatus bit is set.

Reserved 4:1 0h

GblEn 5 0b If this bit is set, SCI is raised whenever both GblEn and

GblStatus are true.

Reserved 7:6 00b

PwrBtnEn 8 0b If this bit is set, SCI is generated whenever PwrBtnStatus is

true.

Reserved 9 0b

RtcEn 10 0b RTC enable. If this bit is set, SCI is generated whenever

RtcStatus is true.