©2008 Advanced Micro Devices, Inc.

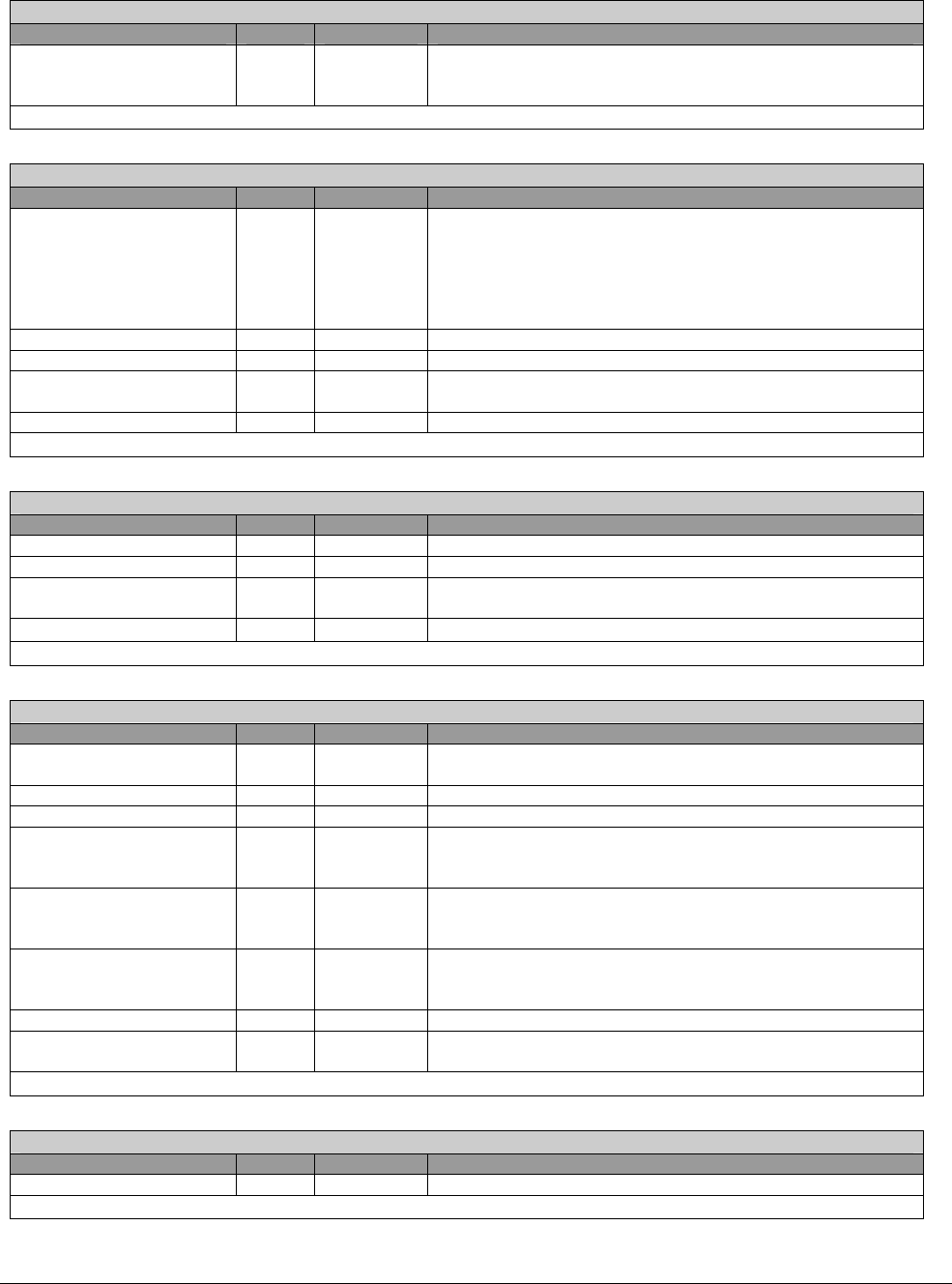

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 157

TPRESET2 - RW – 8 bits - [PM_Reg: 52h]

Field Name Bits Default Description

PopUpReqHoldEn

(Applicable to ASIC

revision A21 and above)

7 0b Setting this bit to 1 will cause the pop-up request from the

NB, or from inside of the SB, to be captured and held until the

minimum LDTSTP# assertion time has expired.

TPRESET2 register

TESTENABLE - RW – 8 bits - [PM_Reg: 53h]

Field Name Bits Default Description

T32_64 0 0b Timing parameter used for C3 state in P4 system.

If set, the time from the reception of STOP_GNT# to SLP#

will be ~128 A-Link clocks. When it is cleared, the timing will

be ~64 A-Link clocks. Timing for CPU_STP#/PCI_STP# is

controlled similarly, except the value is 192 or 96 A-Link

clocks respectively when the bit is set or cleared.

Reserved 2:1 00b

SMI_Disable 3 0b When set, SMI# generation will be disabled

Sel_wakeclk 4 0b Test feature: set 1 to use OSC as the wake up clock;

otherwise, use RTC CLK as the wake up clock

Reserved 7:5 000b

TESTENABLE register

PWRBTTN_CLR - RW – 8 bits - [PM_Reg: 54h]

Field Name Bits Default Description

TFATAL_CLR 0 0b Write 1 to clear the TFATAL status bit

PWRBTTN_CLR 1 0b Write 1 to clear the Power Button status bit

SHUTDOWN_CLR 2 0b Write 1 to clear the SHUTDOWN#/GPIO5/SMARTVOLT2

status bit

Reserved 7:3 0000_0b

PWRBTTN_CLR register

SoftPciRst – RW – 8 bits – [PM_Reg:55h]

Field Name Bits Default Description

SoftPciRstEn 0 1b This bit enables both the soft PCIRST and the THRMTRIP

function.

Gate_HpetIrq 1 0b Set to 1 to let HPET enable bit to control IRQ output

UserResetEnable 2 1b When set, GPM7 becomes user reset pin.

PCIeNative

(Applicable to ASIC

revision A21 and above)

3 0b Setting this bit to 1 will cause PCIeHotPlug PCIePme and

WakeAsGevent status to not be set by corresponding events

as required by PCIe native mode.

PCIeWakeMask

(Applicable to ASIC

revision A21 and above)

4 0b Setting this bit will cause PCIEXP_WAKE_STS and

PCIEXP_WAKE_DIS to not be visible as required by WinXP.

PCIeWakeNoSci

(Applicable to ASIC

revision A21 and above)

5 0b Setting this bit will cause PCIEXP_WAKE_STS to not

generate SCI.

SoftPciRst 6 0b Setting bit 6 will cause a PCIRST.

HideHpetBar 7 0b Set to1 to make Bar1 in SM configuration space invisible (can

Not write and always read 0)

SoftPciRst register

Reserved – 8 bits - [PM_Reg: 56h]

Field Name Bits Default Description

Reserved 7:0 00h

Reserved