©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual Proprietary Page 209

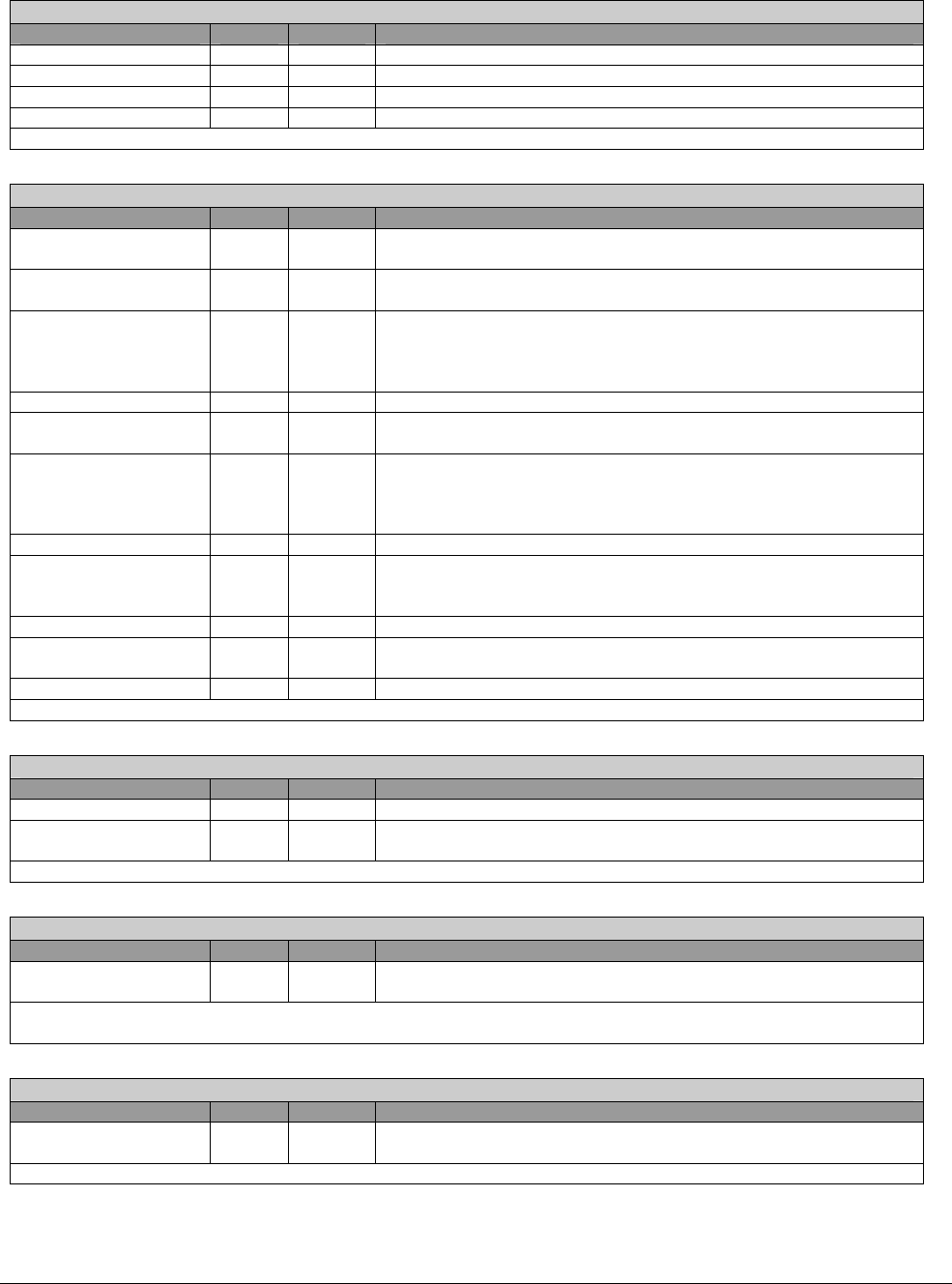

Output DMA DT Size and State- R - 32 bits - [MEM_Reg: 48h]

Field Name Bits Default Description

Out DMA DT size 15:0 0000h Data size of DT for Output DMA.

Reserved 25:16 000h

out DMA state 28:26 0h Current state of out DMA

Reserved 31:29 0h

Output DMA DT Size & State Register:

SPDIF Command- RW - 32 bits - [MEM_Reg: 4Ch]

Field Name Bits Default Description

Spdif valid bit 0 0b The value of this bit will go to bit[28] of each enabled sub-frame on

SPDIF_OUT bus, which is the valid bit for that subframe.

Spdif user bit 1 0b The value of this bit will go to bit[29] of each enabled sub-frame on

SPDIF_OUT bus, which is the user bit for that subframe.

SPDIF bus mute 2 0b Setting it to 1 will mute the whole SPDIF bus to zero when the next

frame comes. Setting it back to 0 will unmute SPDIF bus when the

next frame comes. Changing of this bit only starts to take effect on

frame boundary.

Reserved 3 0b

LFSR Control 4 0b 0 - Shift direction left.

1 - Shift direction right.

Single channel mode 5 0b 1 - SPDIF operates in the single channel mode (disable second

sub-frame)

0 - SPDIF operates in the 2-channel mode (every sub-frame filed

with data from FIFO)

Reserved 6 0b

Data mute 7 0b When this bit is set to 1, on each subframe of spdif bus, the data

field (bit[27:4]) is set to 0, no matter what data are written to spdif

FIFO.

LFSR Accumulation 15:8 00h LFSR Linear feedback shift Register [Read-only]

SPDIF Threshold 20:16 00h Threshold value for the SPIDF Channel's FIFO. (SPDIF FIFO is

30x28)

Reserved 31:21 000h

SPDIF Command Register: Controls the operation of SPDIF channel.

SPDIF Channel Link List Pointer- RW - 32 bits - [MEM_Reg: 50h]

Field Name Bits Default Description

SPDIF LL ptr enable 0 0b SPDIF Channel Link List Pointer enable

SPDIF LL Pointer 31:1 0000_0

000h

Pointer to the start of the Link List - to the first DT.

SPDIF Channel Link List Pointer Register: Pointer to the start of Link List for the SPDIF channel.

SPDIF Channel DT Start- R - 32 bits - [MEM_Reg: 54h]

Field Name Bits Default Description

SPDIF DT start 31:0 0000_0

000h

SPDIF Channel Discrete Table (DT) Start Pointer

SPDIF channel DT start Pointer Register: Pointer to the start of data associated with current DT for the SPDIF

channel.

SPDIF Channel DT Next- R - 32 bits - [MEM_Reg: 58h]

Field Name Bits Default Description

SPDIF DT next 31:0 0000_0

000h

Pointer to the next DT for the SPDIF channel.

SPDIF channel Next Pointer Register: