©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 114

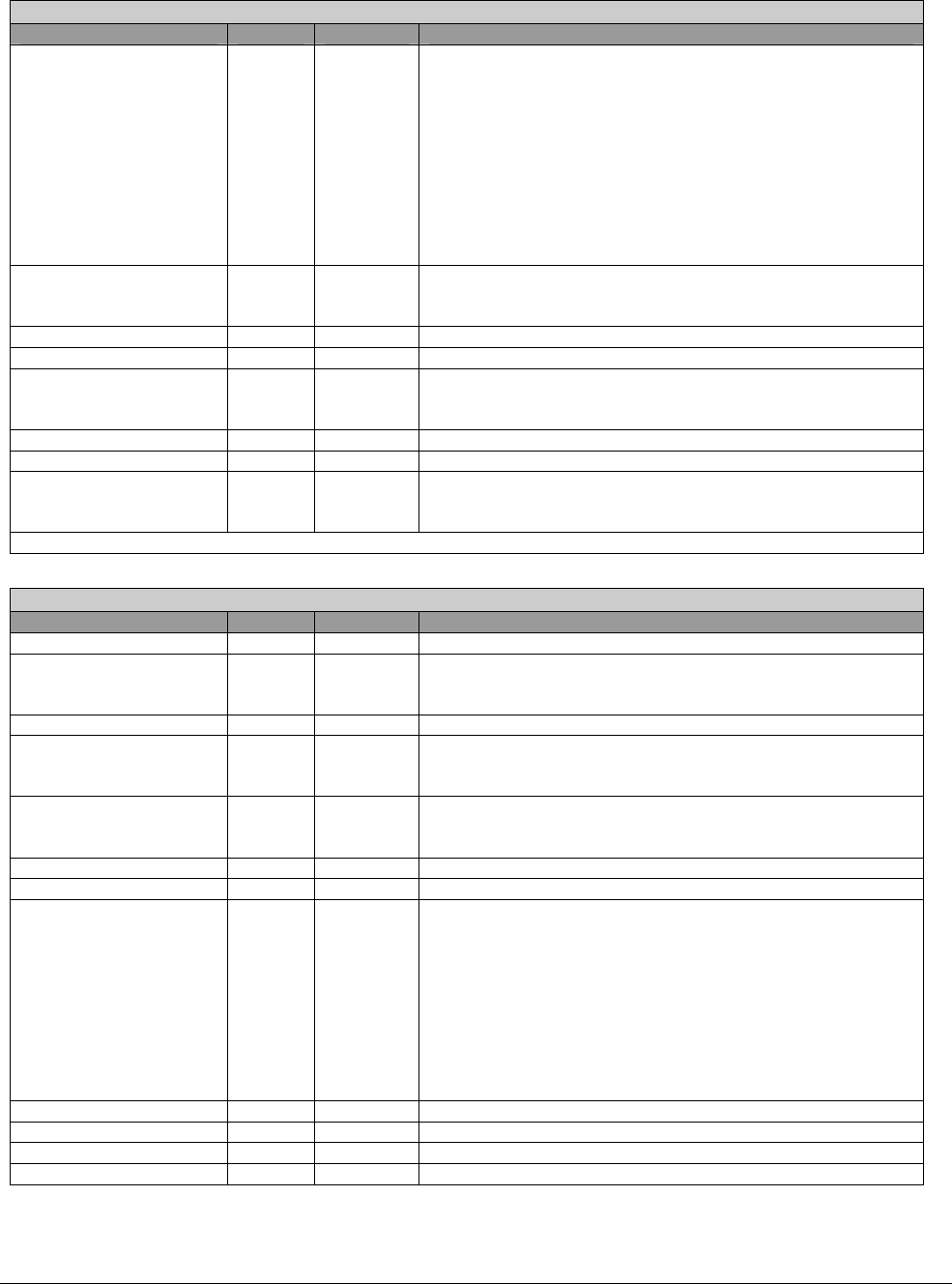

GPIO_12_to_4_Cntrl – RW – 32 bits - [PCI_Reg: A8h]

Field Name Bits Default Description

GPIO_Out 7:0 00h Write 1 to set and 0 to clear each of the GPIO port providing

the corresponding bits [15:8], [25], [31:30] are enabled

Output for GPIO[12:11][9:4]

Bit[0] for GPIO4/SMARTVOLT

Bit[1] for GPIO5/SHUTDOWN/SMARTVOLT2

Bit[2] for GPIO6/GNI#

Bit[3] for GPIO7/VGATE

Bit[4] for GPIO8/DDC1_SDA

Bit[5] for GPIO9/DDC1_SCL

Bit[6] for GPIO11/SPI_DO

Bit[7] for GPIO12/SPI_DI

GPIO_Out_En# 15:8 FFh GPIO output port enable for each of the GPIO port

0: Output = GPIO_Out

1: Output = tristate

GpioIn 23:16 - GPIO input status for each of the GPIO port

GPIO10_Out 24 0b Write 1 to set and 0 to clear GPIO10/SATA_IS0#

GPIO10_Out_En# 25 1b GPIO output port enable for GPIO10/SATA_IS0#

0: Output = GPIO10_Out

1: Output = tristate

GPIO10_Status 26 - GPIO input status for GPIO10/SATA_IS0#

Reserved 29:27 000b

GPIO_Enable 31:30 0h GPIO function enable for GPIO[12:11]

0: GPIO disabled

1: GPIO enabled

GPIO_12_to_4_Cntrl register

SATA_Cntrl - RW – 16 bits - [PCI_Reg: ACh]

Field Name Bits Default Description

GPIO67_Out 0 0b Write 1 to set and 0 to clear GPIO67/SATA_ACT#

GPIO67_Out_En# 1 1b GPIO output port enable for GPIO67/SATA_ACT#

0: Output = GPIO67_Out

1: Output = tristate

GPIO67_Status 2 - GPIO input status for GPIO67/SATA_ACT#

GPIO67_Enable 3 0b GPIO function enable for GPIO67/SATA_ACT#

0: GPIO disabled

1: GPIO enabled

SMI_CMD_action

4 1b If this bit is enabled, SMI_CMD or SLP_trap will cause SMI

being sent to host regardless of EOS status. Otherwise, SMI is

sent only when EOS=1.

Reserved 7:5 0h

SataEnable 8 1b SATA enable

SataSmbusCfg 10:9 00b SATA SMBus configuration.

00: Reserved

01: Disable SATA SMBus

10: Reserved

11: Enable SATA SMBu

There is only one SATA SMBus (I2C) interface for the two

SATA controllers. The SATA I2C interface is only used for

characterization purposes. Use either an external I2C master

or the on-chip SMBus as I2C master to talk to the SATA I2C

target.

Reserved 12:11 00b

SataPsvEn 13 1b SATA power saving enable

Reserved 14 0b

HiddenMsiEnable 15 0b Setting this bit will make PCI_Reg:B0h, bit 16 to show up as 1.