©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 23

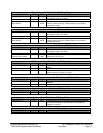

PHY Port3 Control - RW- 32 bits - [PCI_Reg:94h]

Field Name Bits Default Description

Port3 PHY 23:0 B40014h PHY port3 fine-tune register.

TX main swing 4:0 10100b Port3 Tx driving swing[4:0] is valid at SATA 1.5G.

Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Nominal Output

1 0 0 0 0 400mv

1 0 0 1 0 450mv

1 0 1 0 0 500mv

1 0 1 1 0 550mv

1 1 0 0 0 600mv

1 1 0 1 0 650mv

1 1 1 0 0 700mv

1 1 1 1 0 750mv

Note: This applies to all the ASIC Revisions A11 and above.

TX pre-emphasis driver

swing

7:5 000b Port3 Tx driving swing[7:5] is valid for both SATA 3G and

1.5G. It sets the TX pre-emphasis driver strength. The user

can program the optimum pre-emphasis value for each SATA

port if TX pre-emphasis enable bit turned on.

Bit 7 Bit 6 Bit 5 pre-emphasis amount

0 0 0 0mv

0 0 1 25mv

0 1 0 50mv

0 1 1 75mv

1 0 0 100mv

1 0 1 125mv

1 1 0 150mv

1 1 1 175mv

Note: This applies to all the ASIC Revisions A11 and above.

TX pre-emphasis enable 13 0b Turns on port3 TX pre-emphasis output

1: Enable pre-emphasis

0: Disable pre-emphasis

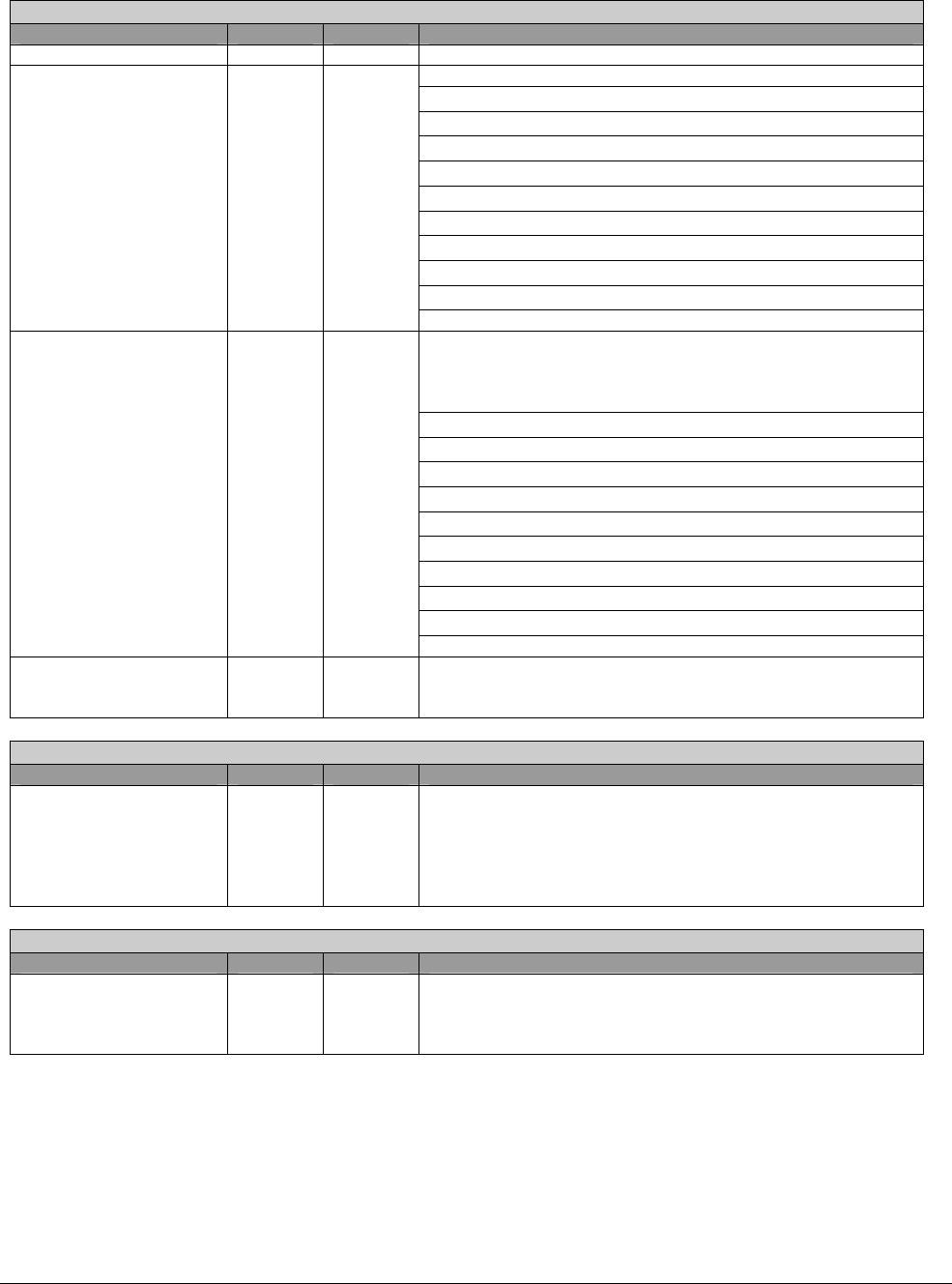

BIST Pattern Count - RW - 32 bits - [PCI_Reg:C0h]

Field Name Bits Default Description

BIST Pattern Count 31:0 0000_20

00h

This count specifies how many Octal WORD pattern need to

be checked before BIST Done bit be set. This count value is

used fro all the 4 ports. 400h default value would be used for

tester, which means 32K DWORD pattern would be compared

for BIST test. Value of “0000_0000”h means the maximum

patterns (16,000, 000, 000) checked.

PCI Target Control TimeOut Counter - RW – 8 bits - [PCI_Reg:C4h]

Field Name Bits Default Description

PCI Target Control

TimeOut Count

7:0 80h This register is used for programming the PCI Target Control

TimeOut Count used to clear any stale target commands to

the hosts controller. Granularity is 15.5us (Count * 15.5 us)

The counter will be disabled if the count is programmed to 0x0.