©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 25

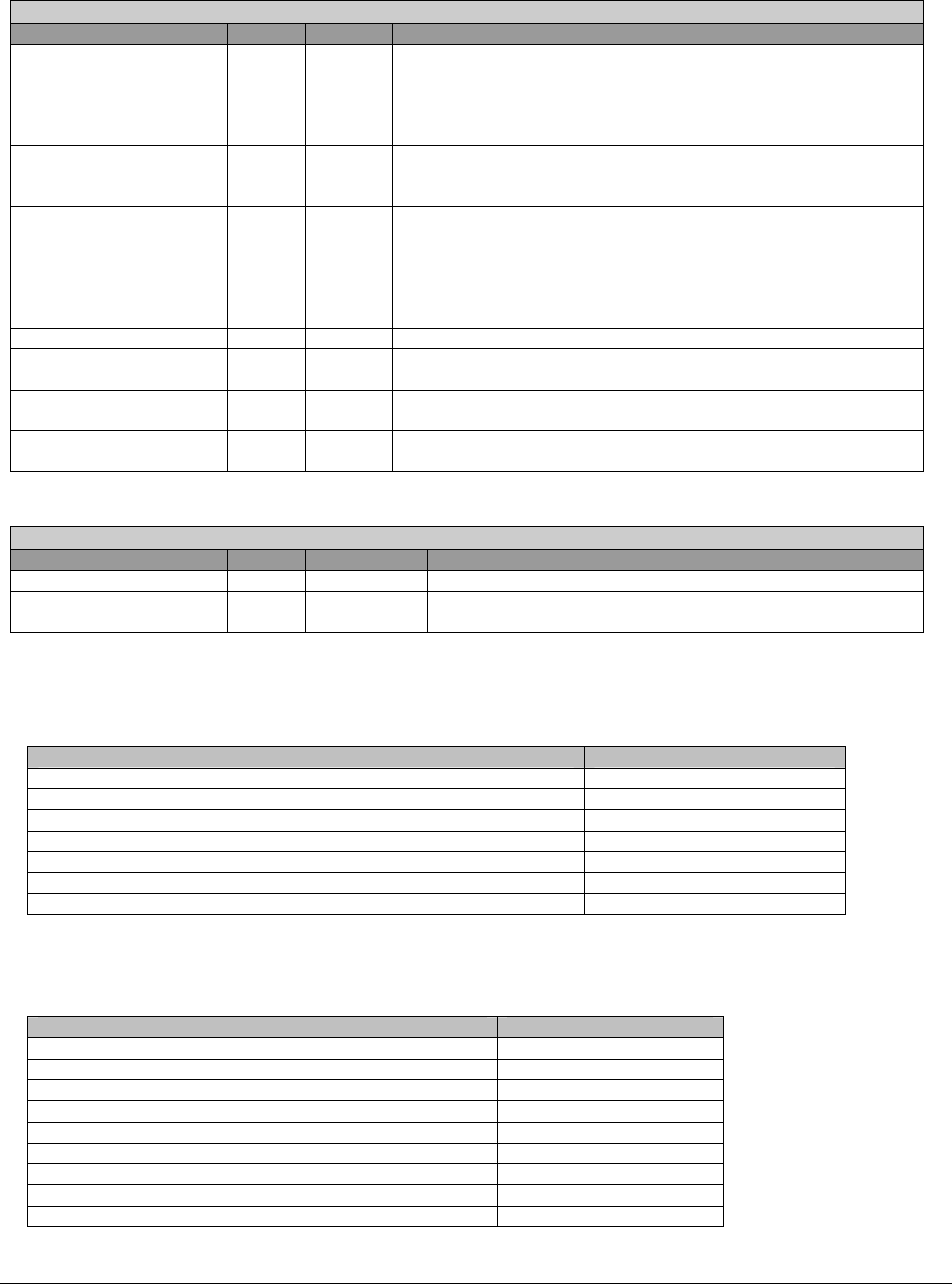

Bus-master IDE Status - RW- 8 bits - [IO_Reg: BAR4 + 02/0Ah]

Field Name Bits Default Description

Bus Master Active 0 0b Bus Master IDE active. This bit is set to 1 when bit 0 in the Bus

Master IDE command address register is set to 1. The IDE host

controller sets this bit to 0 when the last transfer for a region is

performed. This bit is also set to 0 when bit 0 of the Bus Master

IDE command register is set to 0.

Bus Master DMA Error 1 0b IDE DMA error. This bit is set when the IDE host controller

encounters a target abort, master abort, or Parity error while

transferring data on the PCI bus. Write ‘1’ clears this bit

IDE Interrupt 2 0b IDE Interrupt. Indicates when an IDE device has asserted its

interrupt line. IRQ14 is used for the Primary channel and IRQ15 is

used for the secondary channel. If the interrupt status bit is set to

0, by writing a 1 to this bit while the interrupt line is still at the

active level, this bit remains 0 until another assertion edge is

detected on the interrupt line.

Reserved 4:3 Reserved.

Master Device DMA

Capable

5 0b Device 0 (Master) DMA capable.

Slave Device DMA

Capable

6 0b Device 1 (Slave) DMA capable.

Simplex Only 7 0b Read Only

Simplex only. This bit is hard-wired as 0.

Descriptor Table Pointer - RW- 32 bits - [IO_Reg: BAR4 + 04/0Ch]

Field Name Bits Default Description

Reserved 1:0 0h Reserved. Always read as 0’s.

Descriptor Table Base

Address

31:2 0000_0000h Base Address of Descriptor Table. These bits correspond to

Address [31-02].

2.1.4 BAR5 Registers

These are the AHCI memory map registers. The base address is defined through the ABAR (BAR5) register.

Register Name Offset Address

Generic Host Control 00h-23h

Reserved

24h-9Fh

Vendor Specific registers A0h-FFh

Port 0 port control registers 100h-17Fh

Port 1 port control registers 180h-1FFh

Port 2 port control registers 200h-27Fh

Port 3 port control registers 280h-2FFh

2.1.4.1 Generic Host Control

The following registers apply to the entire HBA.

Register Name Offset Address

Host Capabilities(CAP) 00h-03h

Global Host Control(GHC) 04h-07h

Interrupt Status(IS) 08h-0Bh

Ports Implemented(PI) 0Ch-0Fh

Version(VS) 10h-13h

Command Completion Coalescing Control(CCC_CTL) 14h-17h

Command Completion Coalescing Ports(CCC_PORTS) 18h-1Bh

Enclosure Management Location(EM_LOC) 1Ch-1Fh

Enclosure Management Control(EM_CTL) 20h-23h