©2008 Advanced Micro Devices, Inc.

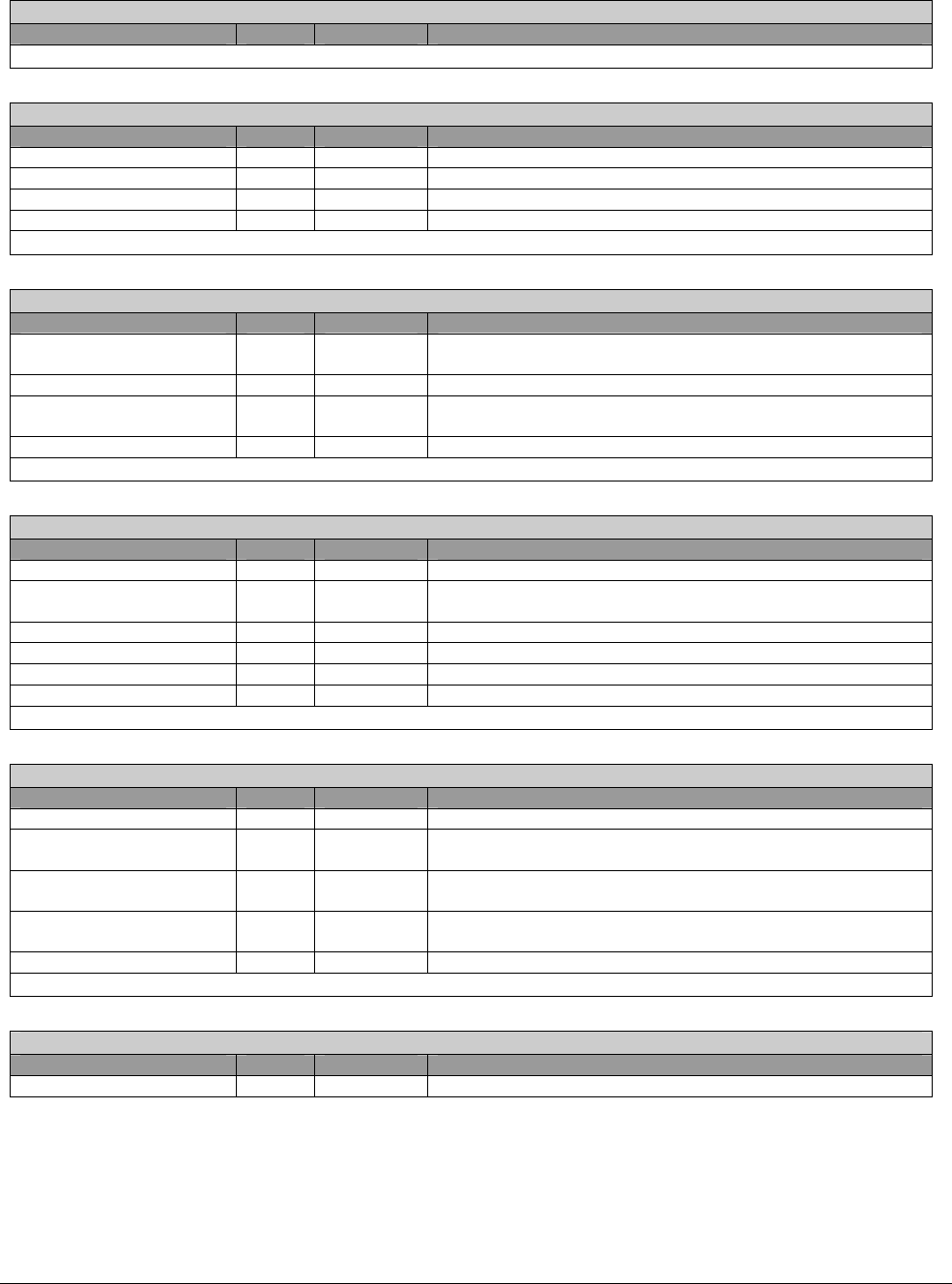

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 167

SMAF1 – RW – 8 bits – [PM_Reg:81h]

Field Name Bits Default Description

SMAF1 register

SMAF2 – RW – 8 bits – [PM_Reg:82h]

Field Name Bits Default Description

S1SMAF 2:0 011b System management action field for S1 STPCLK message

Reserved 3 0b

S3SMAF 6:4 100b System management action field for S3 STPCLK message

Reserved 7 0b

SMAF2 register

SMAF3 – RW – 8 bits – [PM_Reg:83h]

Field Name Bits Default Description

NSSMAF 2:0 101b System management action field for Normal Throttling

STPCLK message

Reserved 3 0b

TTSMAF 6:4 101b System management action field for Thermal Throttling

STPCLK message

Reserved 7 0b

SMAF3 register

WakePinCntl – RW – 8 bits – [PM_Reg:84h]

Field Name Bits Default Description

WakePinEnable 0 1b Set to 1 to enable wakeup from WAKE#/GEVENT#[8] pin

WakePinAsGEvent 1 0b Set to 1 to use WAKE#/GEVENT#[8] pin as GEvent, replacing

GPIO0

WakeOut 2 0b Output data for wake pin

WakeOutEnB 3 1b Output enable for wake pin (active low)

WakePinStatus 4 0b Input status for wake pin

Reserved 7:5 000b

WakePinCntl register

CF9Rst – RW – 8 bits – [PM_Reg:85h]

Field Name Bits Default Description

Reserved 0 0b

SysRst 1 0b 0: Send INIT HT message

1: Reset as specified by bit3

RstCmd 2 0b Write with 1 to generate reset as specified by bit[3,1]

Write only, always read as 0

FullRst 3 0b 0: Assert reset signals only

1: Place system in S5 state for 3 to 5 seconds

Reserved 7:4 0h

CF9Rst register

ThermThrotCntl – RW – 8 bits – [PM_Reg:86h]

Field Name Bits Default Description

Therm2SecDelay 0 0b Enable 2 second delay for thermal clock throttle