©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 231

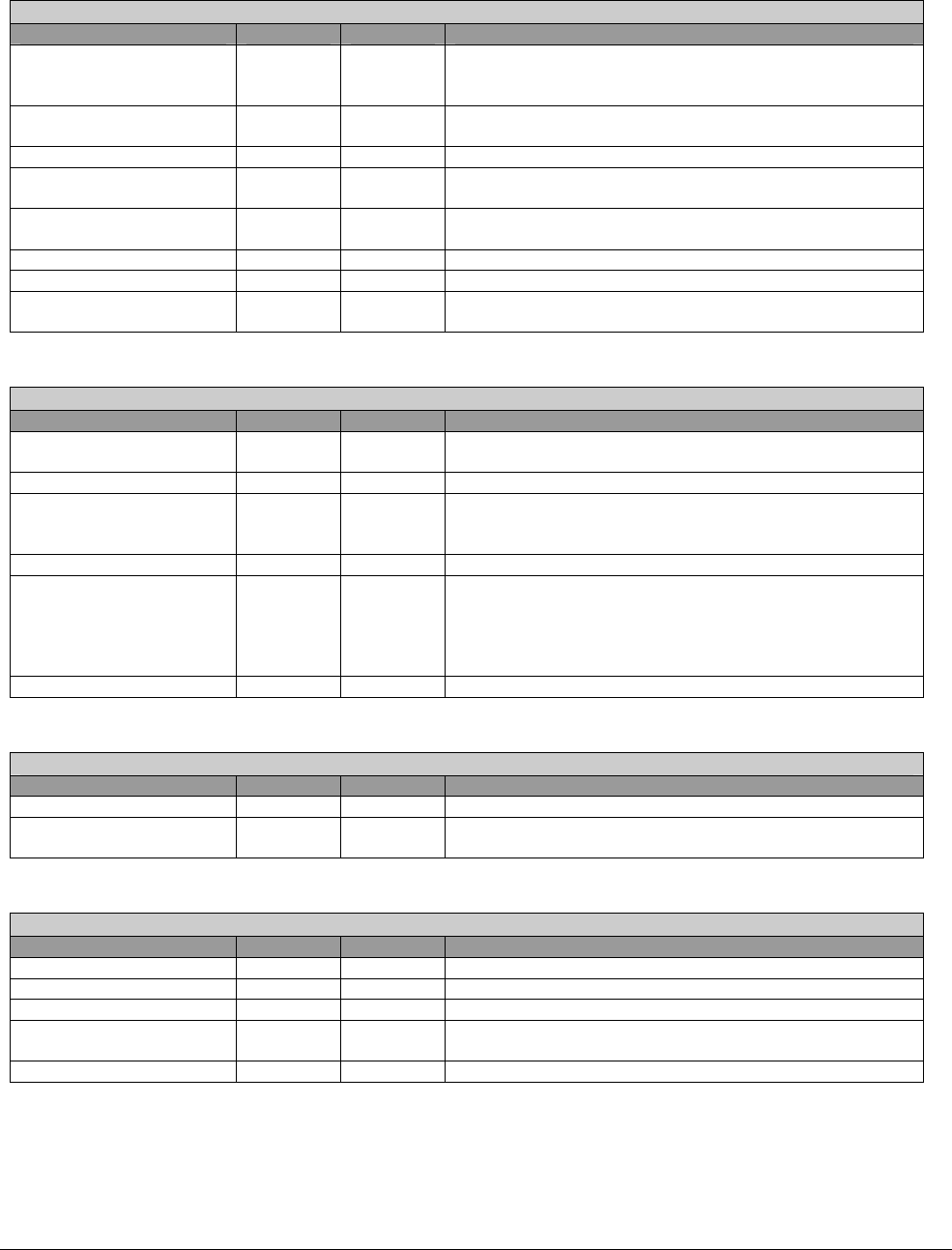

Power Management Capabilities – R – 16 bits – [PCI_Reg: 52h]

Field Name Bits Default Description

Version 2:0 010b Hardwired to 010b. Indicates this function complies with

Revision 1.1 of the PCI Power Management Interface

Specification

PME Clock 3 0b Hardwired to “0”. Indicates that no PCI clock is required for

the function to generate PME#.

Reserved 4 0b Reserved

Device Specific

Initialization

5 0b Hardwired to “0”. Indicates that no device specific

initialization is required.

Aux Current 8:6 001b Hardwired to 001b. Indicates 55mA maximum suspend well

current is required in the D3cold state.

D1 Support 9 0b Hardwired to “0”. Indicates D1 state is not supported.

D2 Support 10 0b Hardwired to “0”. Indicates D2 state is not supported.

PME Support 15:11 11001b Hardwired to 11001b. Indicates PME# can be generated

from D0 and D3 states.

Power Management Control/Status – RW – 32 bits – [PCI_Reg: 54h]

Field Name Bits Default Description

Power State 1:0 0h This field is used both to determine the current power state

and to set a new power state of the HD Audio controller.

Reserved 7:2 00h Reserved

PME Enable 8 0b Enables the function to assert PME#.

This bit is in resume well and only cleared on power-on

reset.

Reserved 14:9 00h Reserved

PME Status 15 0b This bit set when HD Audio controller asserts the PME#

signal, it is independent of the PME Enable bit.

Writing a “1” clears this bit.

This bit is in resume well and only cleared on power-on

reset.

Reserved 31:16 0000h Reserved

MSI Capability ID – R – 16 bits – [PCI_Reg: 60h]

Field Name Bits Default Description

Capability ID 7:0 05h Hardwired to 05h. Indicates MSI Capability.

Next Capability Pointer 15:8 00h Hardwired to “0”. Indicates this is the last capability

structure in the list.

MSI Message Control – RW - 16 bits – [PCI_Reg: 62h]

Field Name Bits Default Description

MSI Enable 0 0b Enables MSI if set to “1”.

Multiple Message Capable 3:1 0h Hardwired to “0”. Indicates support for one message only.

Multiple Message Enable 6:4 0h Hardwired to “0”. Indicates support for one message only.

64 Bit Address Capability 7 1b Hardwired to “1”. Indicates the ability to generate 64-bit

message address.

Reserved 15:8 00h Reserved