©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual Proprietary Page 226

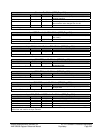

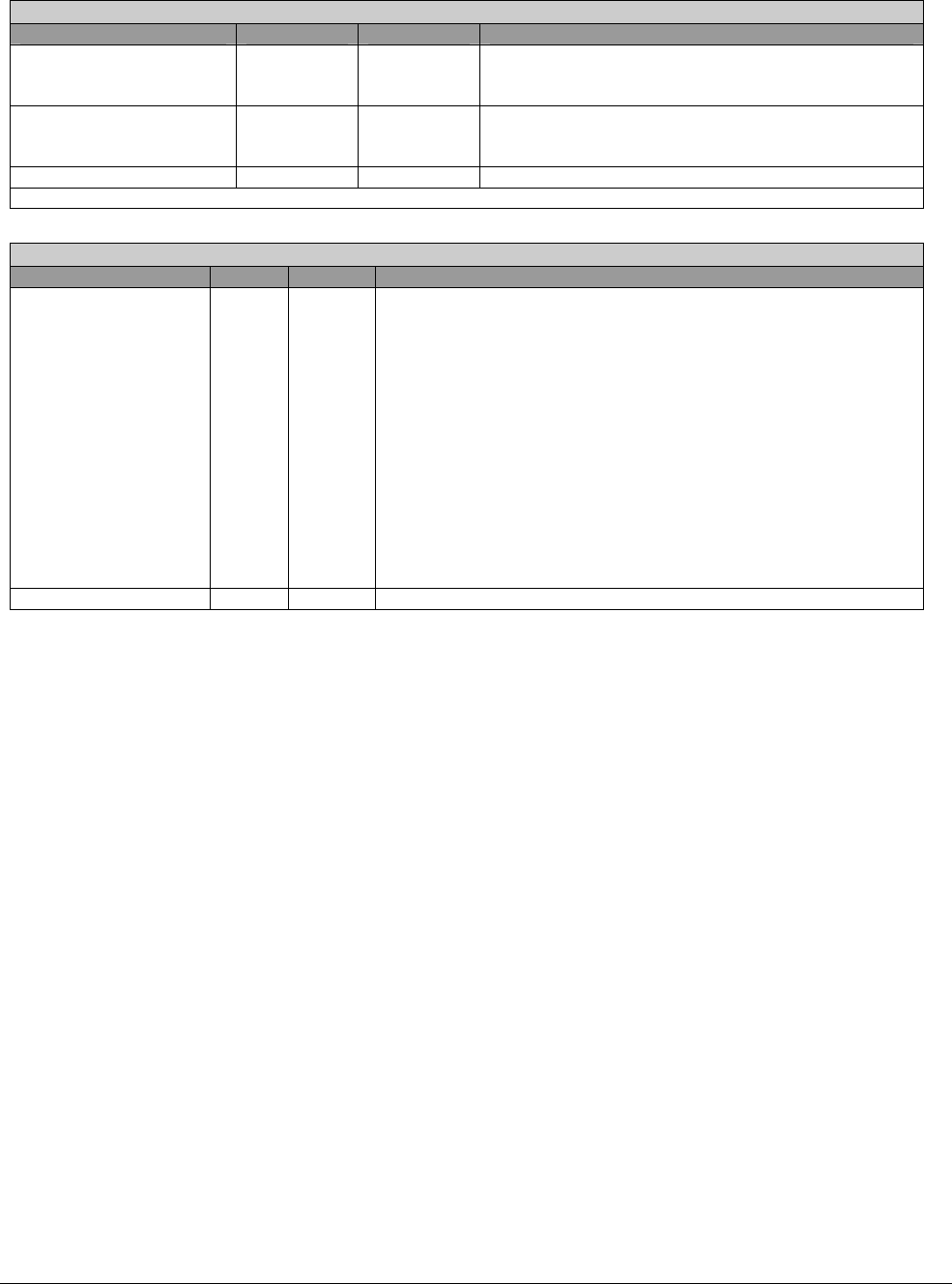

Modem Fifo Flush– W - 32 bits - [MEM_Reg: 88h]

Field Name Bits Default Description

Output DMA3 Fifo Flush 2 0b Writing to this bit flushes modem output DMA3 fifo,

i.e., the indexes and Used/Free counts are reset.

Reading this bit returns 0.

Input DMA Fifo Flush 3 0b Writing to this bit flushes modem input DMA fifo, i.e.,

the indexes and Used/Free counts are reset. Reading

this bit returns 0.

Reserved 31:4 0000000h

Modem Fifo Flush Register.

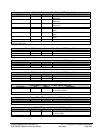

Modem Phy Semaphore Reg- RW - 8 bits - [MEM_Reg: A8h]

Field Name Bits Default Description

Modem Phy

semaphore

0 0b PHY is ready for Modem to access.

0 = PHY is not ready for Modem to access.

1 = PHY is ready for Modem to access.

Modem driver can only accesses PHY register when the read back

value of this bit is ‘1’ after write a ‘1’ to this bit. It is possible the read

back value is ‘0’ after write ‘1’ which mean PHY is not ready for

Modem to access. Since PHY can be accessed by both audio &

modem controllers, the bit is used by modem driver to establish

semaphore handshake with audio driver.

Driver is also responsible to clear the bit after its PHY read/write

access.

Note: The driver can check Mem_reg 0x10[8] which indicates a PHY

read access completion. For writing to PHY, the driver can clear the

semaphore bit after the write command.

Reserved 7:1 00h