©2008 Advanced Micro Devices, Inc.

LPC ISA Bridge (Device 20, Function 3)

AMD SB600 Register Reference Manual Proprietary Page 252

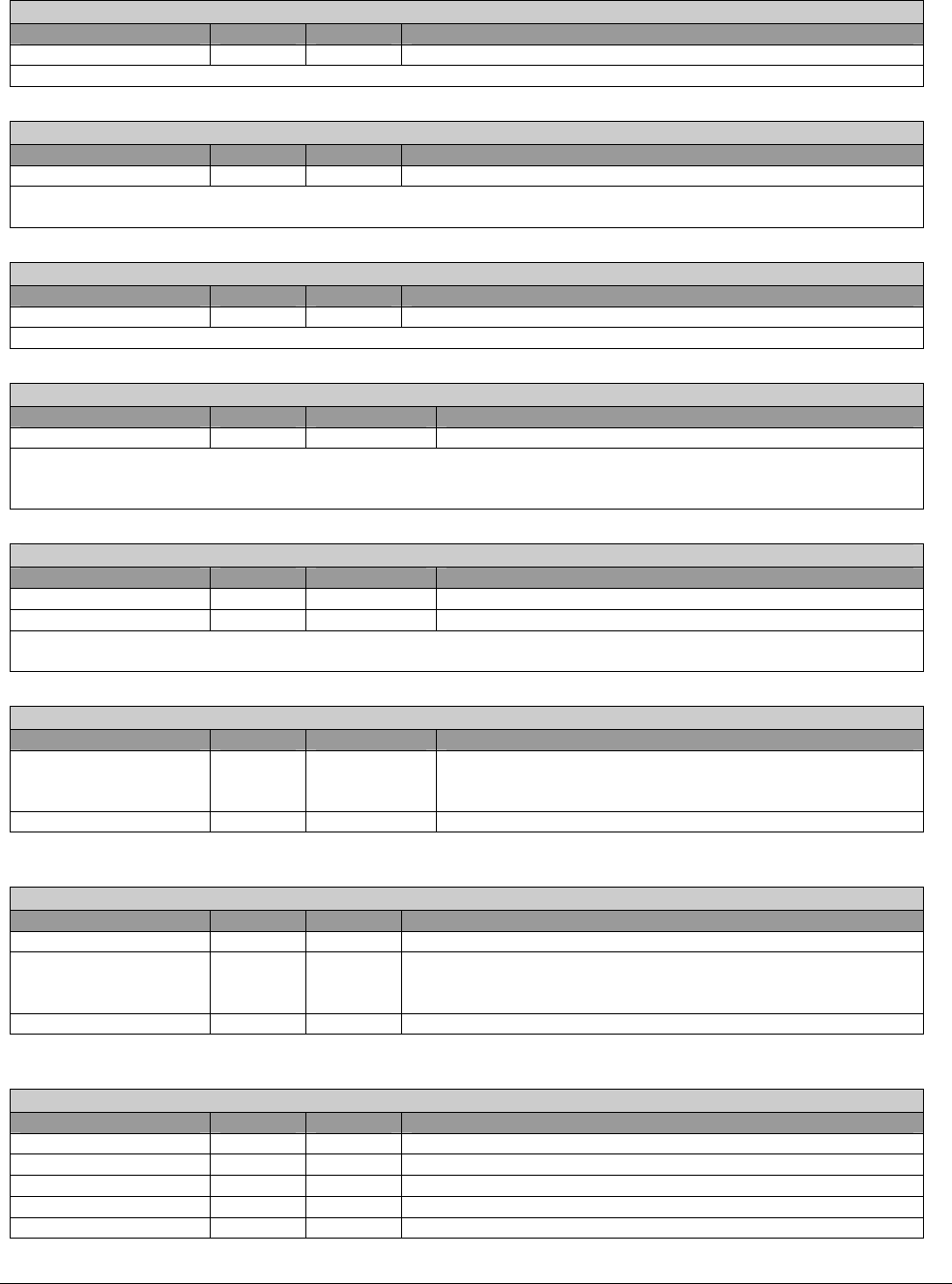

Latency Timer - R - 8 bits - [PCI_Reg: 0Dh]

Field Name Bits Default Description

Latency Timer 7:0 00h Latency Timer.

Latency Timer Register: This register specifies the value of the Latency Timer in units of PCICLKs.

Header Type - R - 8 bits - [PCI_Reg: 0Eh]

Field Name Bits Default Description

Header Type 7:0 80h Header Type.

Header Type Register: This register identifies the type of the predefined header in the configuration space. Since

THE SB600 is a multifunction device, the most significant bit is set.

BIST- R - 8 bits - [PCI_Reg: 0Fh]

Field Name Bits Default Description

BIST 7:0 00h BIST.

Built-in Self Test Register: This register is used for control and status for Built-in Self Test. LPC has no BIST modes.

Base Address Reg 0- RW* - 32 bits - [PCI_Reg: 10h]

Field Name Bits Default Description

Base Address 0 31:0 FEC0_0000h Base address register 0.

This register is write-only. Reading it always returns 0000_0000h. It has an internal value used as base address for

APIC memory space. Writing to the register will change its internal value, but only bit[31:5] is overwritten, and

bit[4:0] is hardwired to 00000b. The default internal value is FEC0_0000h.

Subsystem ID & Subsystem Vendor ID – RW - 32 bits - [PCI_Reg: 2Ch]

Field Name Bits Default Description

Subsystem Vendor ID 15:0 0000h Subsystem Vendor ID.

Subsystem ID 31:16 0000h Subsystem ID.

This 4-byte register is a write-once & read-only afterward register. The BIOS writes this register once (all 4 bytes at

once) and software reads its value (when needed).

Capabilities Pointer - R - 32 bits - [PCI_Reg: 34h]

Field Name Bits Default Description

Capabilities Pointer 7:0 00h When reg0x78[1] (msi on) is 0, this field reads 0; when

reg0x78[1] is 1, this field reads 80h, pointing to the starting

address of MSI capability register

Reserved 31:8 000000h

PCI Control - RW - 8 bits - [PCI_Reg: 40h]

Field Name Bits Default Description

Reserved 1:0 0h

DMA Enable 2 0b Setting it to 1 enables lpc DMA cycle. Note: 32-bit DMA is not

supported. Transfer size: Channels 0-3: 8 bits, channels 5-7: 16

bits.

Reserved 7:3 00h

IO Port Decode Enable Register 1- RW - 8 bits - [PCI_Reg: 44h]

Field Name Bits Default Description

Parallel Port Enable 0 0 0b Port enable for parallel port, 378-37fh

Parallel Port Enable 1 1 0b Port enable for parallel port, 778-77fh

Parallel Port Enable 2 2 0b Port enable for parallel port, 278-27fh

Parallel Port Enable 3 3 0b Port enable for parallel port, 678-67fh

Parallel Port Enable 4 4 0b Port enable for parallel port, 3bc-3bfh