©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 149

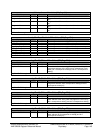

AcpiPm1CntBlkHi - RW – 8 bits - [PM_Reg: 23h]

Field Name Bits Default Description

AcpiPm1CntBlkHi register.

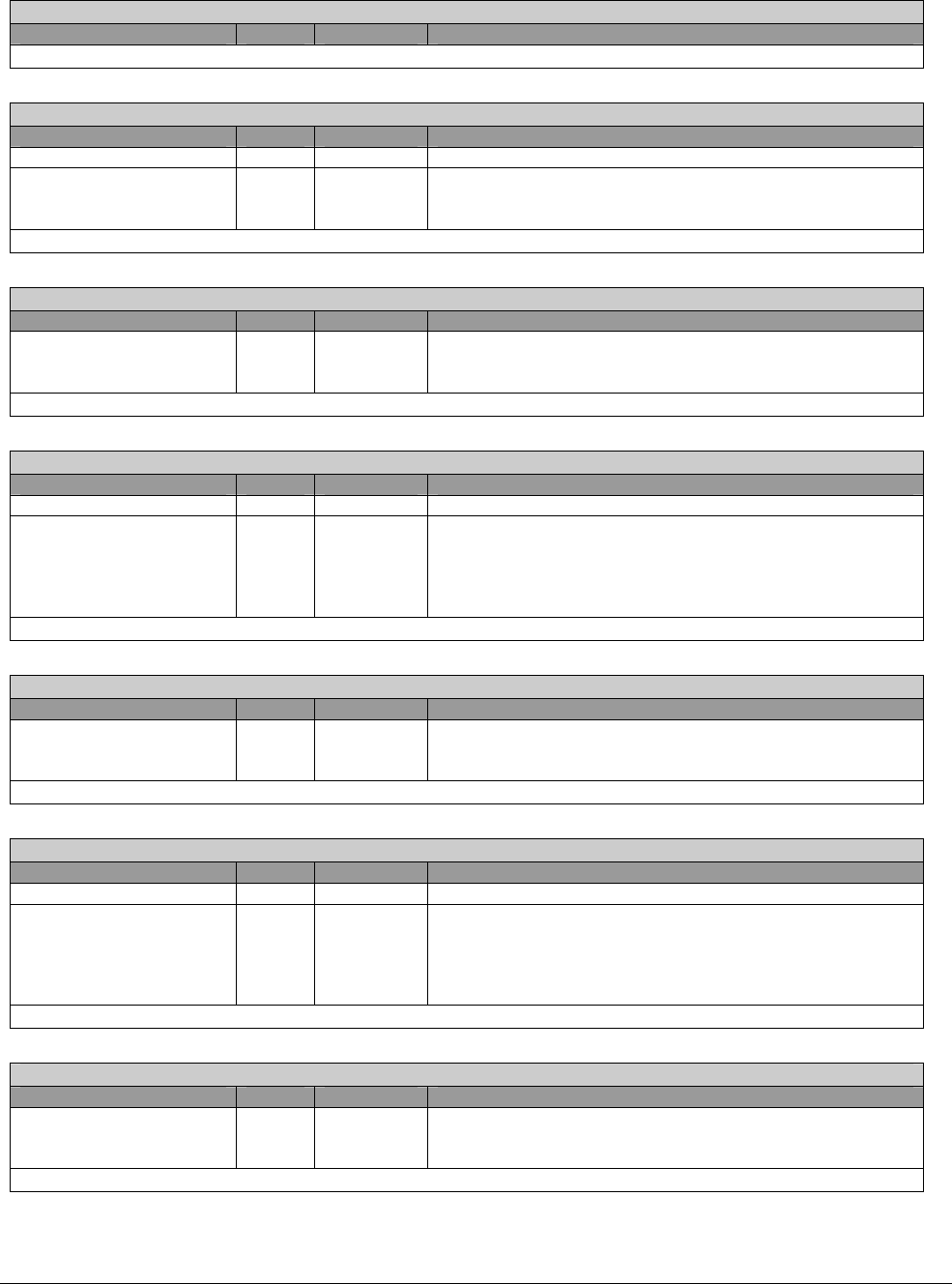

AcpiPmTmrBlkLo - RW – 8 bits - [PM_Reg: 24h]

Field Name Bits Default Description

Reserved 0 0b

AcpiPmTmrBlkLo 7:1 00h These bits define the least significant byte of the 16 bit I/O

base address of the ACPI power management Timer block.

Bit 1 corresponds to Addr[1] and bit 7 corresponds to Addr[7].

AcpiPmTmrBlkLo register.

AcpiPmTmrBlkHi - RW – 8 bits - [PM_Reg: 25h]

Field Name Bits Default Description

AcpiPmTmrBlkHi 7:0 00h These bits define the most significant byte of the 16 bit I/O

base address. Bit 0 corresponds to Addr[8] and bit 7

corresponds to Addr[15].

AcpiPmTmrBlkHi register.

CpuControlLo - RW – 8 bits - [PM_Reg: 26h]

Field Name Bits Default Description

Reserved 2:0 000b

CpuControlLo 7:3 00h These bits define the least significant byte of the 16 bit I/O

base address of the ACPI power management CPU Control

block. Bit 3 corresponds to Addr[3] and bit 7 corresponds to

Addr[7]. Addr[2:0] are ignored because this register block is 6

byte long.

CpuControlLo register.

CpuControlHi - RW – 8 bits - [PM_Reg: 27h]

Field Name Bits Default Description

CpuControlHi 7:0 00h These bits define the most significant byte of the 16 bit I/O

base address. Bit 0 corresponds to Addr[8] and bit 7

corresponds to Addr[15].

CpuControlHi register.

AcpiGpe0BlkLo - RW – 8 bits - [PM_Reg: 28h]

Field Name Bits Default Description

Reserved 1:0 00b

AcpiGpe0BlkLo 7:2 00h These bits define the least significant byte of the 16 bit I/O

base address of the ACPI power management General

Purpose Event block. Bit 2 corresponds to Addr[2] and bit 7

corresponds to Addr[7]. Addr[1:0] are ignored because this

register block is 4 byte long.

AcpiGpe0BlkLo register.

AcpiGpe0BlkHi - RW – 8 bits - [PM_Reg: 29h]

Field Name Bits Default Description

AcpiGpe0BlkHi 7:0 00h These bits define the most significant byte of the 16 bit I/O

base address. Bit 0 corresponds to Addr[8] and bit 7

corresponds to Addr[15].

AcpiGpe0BlkHi register.