©2008 Advanced Micro Devices, Inc.

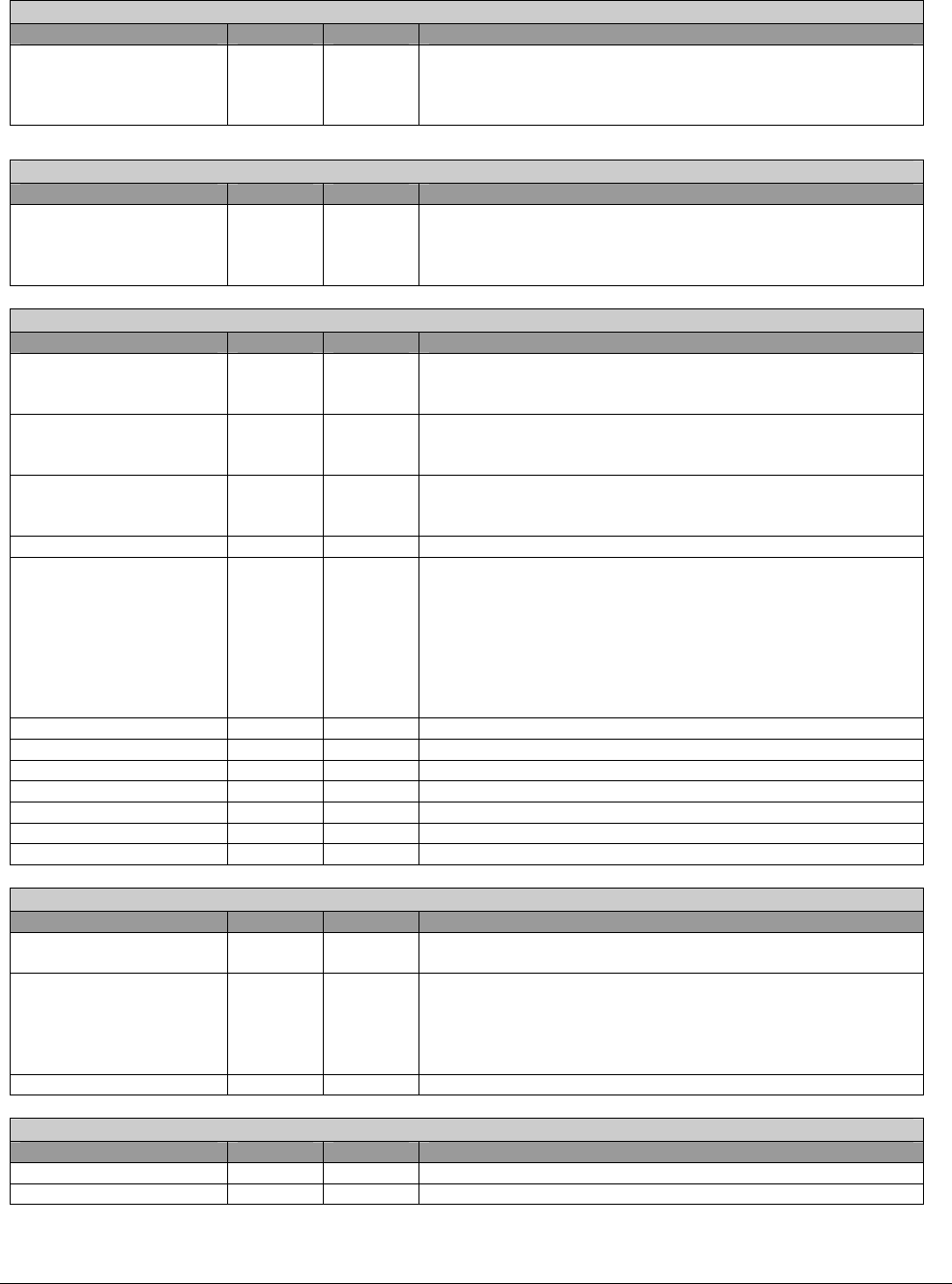

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 18

Min_gnt - R - 8 bits - [PCI_Reg:3Eh]

Field Name Bits Default Description

Minimum Grant 7:0 00h This register specifies the desired settings for how long of a

burst the SATA controller needs. The value specifies a period

of time in units of ¼ microseconds.

Hard-wired to 0’s and always read as 0’s.

Max_latency - R - 8 bits - [PCI_Reg:3Fh]

Field Name Bits Default Description

Maximum Latency 7:0 00h This register specifies the Maximum Latency time required

before the SATA controller as a bus-master can start an

accesses

Hard-wired to 0’s and always read as 0’s.

Misc Control - RW - 32 bits - [PCI_Reg:40h]

Field Name Bits Default Description

Subclass code write

Enable

0 0b Once set, Program Interface register (PCI_Reg:09h), subclass

code register (PCI_Reg:0Ah) and Multiple Message Capable

bits (PCI_Reg50h[19:17]) can be programmable.

Disable Dynamic Sata

Memory Power Saving

1 0b When clear, dynamic power saving function for SATA internal

memory macros will be performed to reduce power

consumption.

Enable dynamic Sata

Core Power Saving

2 0b When set, dynamic power saving function for SATA core clock

will be performed during partial/slumber mode to reduce power

consumption.

Reserved 3 Reserved.

Disable Speed up XP

Boot

4 0b When clear, it fastens XP boot up in IDE mode. However, this

bit needs to be set, when enable SATA partial/slumber power

function is in IDE mode.

When set, the SATA partial/slumber power function can be

enabled in IDE mode, but the BIOS IO trap is needed to speed

up XP boot-up in IDE mode.

Please refer to BAR5 + offset 12C/1Ac/22C/2AC[11:8] for the

SATA partial/slumber modes that are allowed.

Reserved 5 0b Reserved

Reserved 15:6 Reserved.

Disable port0 16 0b When set, port0 is disabled and port0 clock is shut down.

Disable port1 17 0b When set, port1 is disabled and port1 clock is shut down.

Disable port2 18 0b When set, port2 is disabled and port2 clock is shut down.

Disable port3 19 0b When set, port3 is disabled and port3 clock is shut down.

Reserved 31:20 Reserved.

Watch Dog Control And Status - RW - 16 bits - [PCI_Reg:44h]

Field Name Bits Default Description

Watchdog Enable 0 0b Set this bit to enable the watchdog counter for all the PCI

down stream transaction.

Watchdog Timeout

Status

1 0b Watchdog Counter Timeout Status bit. This bit indicates that

the watchdog counter has expired for PCI down stream

transaction and the transaction got aborted due to counter has

expired.

Software writes 1 to clear the status.

Reserved 15:2 Reserved.

Watch Dog Counter - RW - 16 bits - [PCI_Reg:46h]

Field Name Bits Default Description

Watchdog Counter 7:0 80h Specifies the timeout retry count for PCI down stream retries.

Reserved 15:8 Reserved.