©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 106

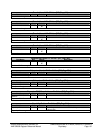

SmartPowerControl1B - RW – 8 bits - [PCI_Reg: 5Dh]

Field Name Bits Default Description

CheckVIN0 0 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN0 has

reached or passed the threshold

CheckVIN1 1 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN1 has

reached or passed the threshold

CheckVIN2 2 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN2 has

reached or passed the threshold

CheckVIN3 3 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN3 has

reached or passed the threshold

CheckVIN4 4 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN4 has

reached or passed the threshold

CheckVIN5 5 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN5 has

reached or passed the threshold

CheckVIN6 6 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN6 has

reached or passed the threshold

CheckVIN7 7 0b If SmartVoltEnable is set and this bit is also set, the

SmartPower function will only assert SmartVolt if VIN7 has

reached or passed the threshold

SmartPowerControl1B register

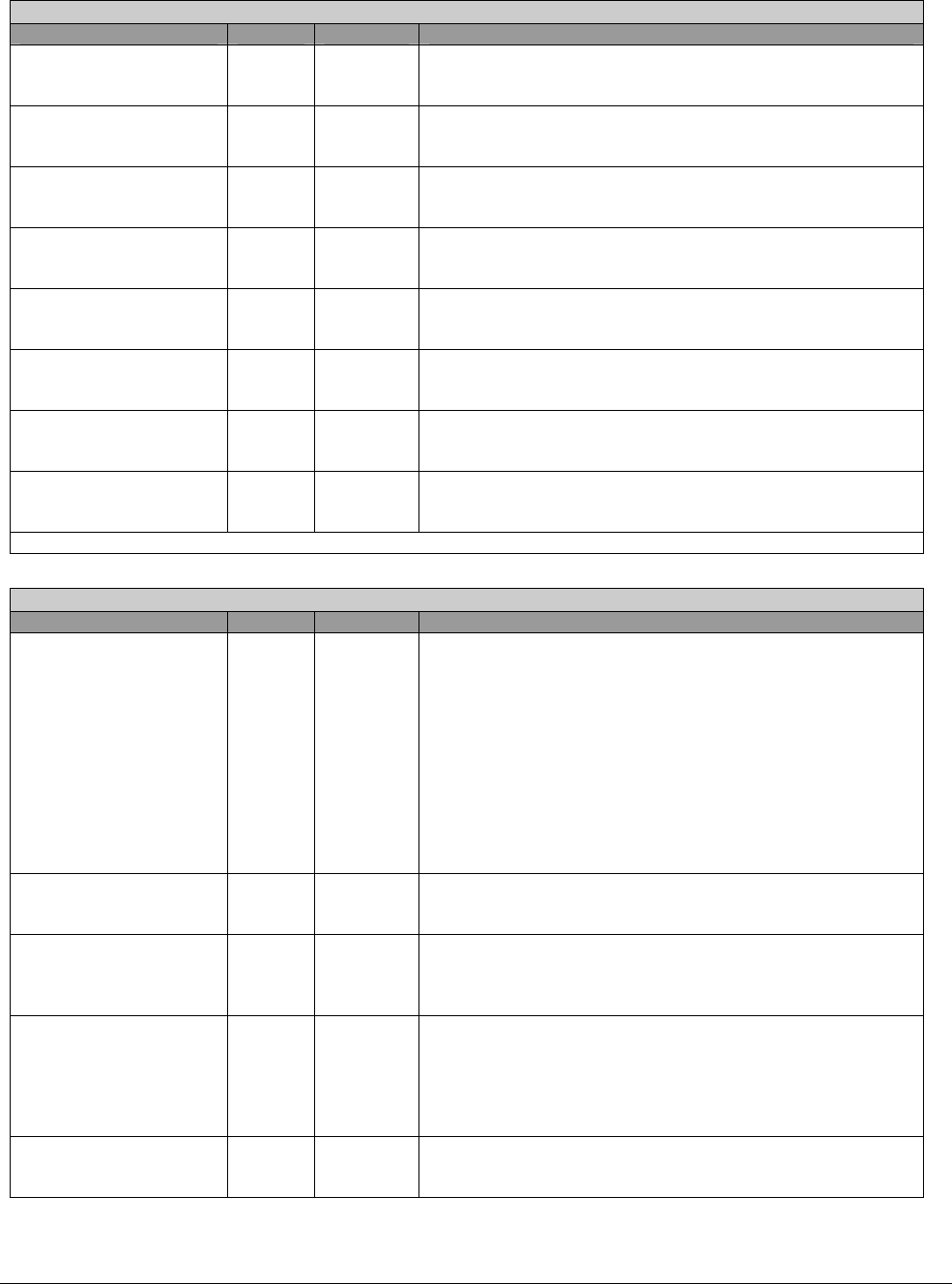

MiscEnable- RW - 8 bits - [PCI_Reg: 62h]

Field Name Bits Default Description

IRQ1_Filter 0 0b Keyboard interrupt filter enable (IRQ1)

Filtering is done so that the first rising edge of IRQ1 would

cause the IRQ1 going to the PIC (8259 programmable

interrupt controller) to go asserted, but subsequent changes to

IRQ1 would not have any effect on the IRQ1 going to the PIC

until a access to the keyboard was done (I/O read

of port 60.

The Main effect is that software could mask IRQ1, do several

accesses / commands to the keyboard controller that

subsequently cause numerous IRQ1’s, do one final I/O read

access of port 60 and know that when IRQ1 was unmasked

that no pending keyboard interrupt would be generated.

IRQ12_Filter 1 0b Mouse Interrupt Filter Enable (IRQ12)

0 – Disable IRQ12 filtering

1 – Enable IRQ12 filtering

K8_INTR 2 0b K8 INTR Enable (BIOS should set this bit after PIC

initialization)

0 – Disable K8 INTR message

1 – Enable K8 INTR message

MT3_Set 3 0b If this bit is set, K8 INTR NMI Message Type field (Bit3) is

forced to be 1; otherwise K8 INTR NMI Message Type is

controlled by MT3_Auto. Recommended method is to use

MT3_Auto bit.. In AMD K8 system, all interrupts are sent to

CPU via messages. In MP base (such as Linux), the message

may need to be in certain format.

MT3_Auto 4 0b If this bit is set, K8 INTR NMI Message Type field (Bit3) is 1 if

APIC is also active; otherwise K8 INTR NMI Message Type is

0