©2008 Advanced Micro Devices, Inc.

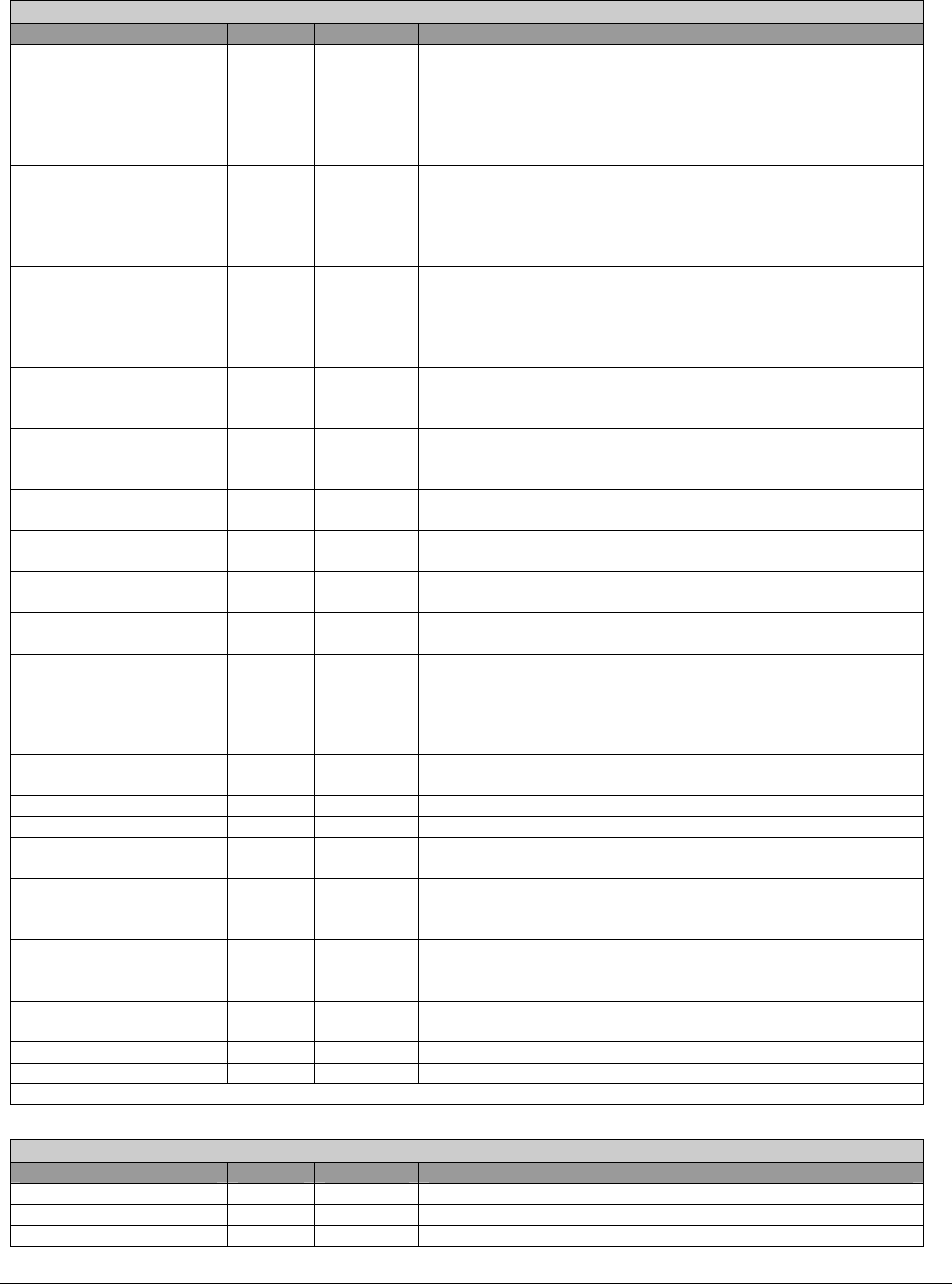

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 108

Features Enable- RW - 32 bits - [PCI_Reg: 64h]

Field Name Bits Default Description

Smi_Gevent_En 12 0b Enable all the events with the capability of doing both SMI#

and SCI to SMI# assertion. If enabled, an assertion at any of

the event inputs will cause SMI# to be asserted if SCI EN is

not set.

0 – Disable

1 – Enable

Intr_block_En 13 0b Applicable in the PIC system. When enabled, it will block any

pending interrupt for approximately 500ns after IntrAck cycle

from the host.

0 – Disable

1 – Enable

ApicPort02Swap 14 0b When set, port 0 of APIC is connected to output of the PIC and

port 2 is connected to IRQ0 (timer0)

When clear, port 0 of APIC is connected to IRQ0 (timer0) and

port 2 is connected to the output of the PIC. Software should

set this bit to conform with MP spec.

UsbSmiEn 15 0b USB SMI# enable:

1 = Enable

0 = Disable

Serr2Smi_En 16 0b Enable SERR# to SMI# assertion

0 – Disable

1 – Enable

Gevent1_en0 17 0b GEVENT group 0 enable (GPM[7] to SMI#/SCI enable) to

ACPI function

Gevent1_en1 18 0b GEVENT group 1 enable (GPM[6] to SMI#/SCI enable) to

ACPI function

Gevent1_en2 19 0b GEVENT group 2 enable (GPM[5:4] to SMI#/SCI enable) to

ACPI function

LpcEnable 20 0b 1 – Enable lpc controller

0 – Disable lpc controller

RtcSelect 21 0b Writing this bit with 1 will toggle the selection between Internal

RTC and External RTC which is set via strap bit.

Reading this bit returns the internal/external mode:

1 = External RTC

0 = Internal RTC

Gevent1_en3 22 0b GEVENT group 3 enable (ExtEvent[1:0], PCIePme) to ACPI

function

Gevent1_en4 23 0b GEVENT group 4 enable (GPM[3:0]) to ACPI function

Reserved 24

DmaVerifyEn 25 0b With LPC is replacing the ISA bus, software needs to set this

bit in order to for DMA verify to work properly

IRQ1MergeEn 26 0b This is the old method to merge the normal IRQ1 with the USB

legacy IRQ1 function. Since this is no longer needed, software

should always leave this bit with 0.

IRQ12MergeEn 27 0b This is the old method to merge the normal IRQ12 with the

USB legacy IRQ12 function. Since this is no longer needed,

software should always leave this bit with 0.

SB_ClkStpEn 29:28 00b SB_ClkStpEn[0] enables PciStpB to stop primary PCI clock.

SB_ClkStpEn[1] enables PciStpB to stop secondary PCI clock

UsbA20En 30 0b USB A20 enable

UsbLegacyIrqEn 31 0b Enable for IRQ1/12 from USB (BIOS should always set it to 1)

Features Enable register

UsbEnable - RW - 8 bits - [PCI_Reg: 68h]

Field Name Bits Default Description

EHCI_enable 0 1b Set to 1 to enable EHCI

OHCI_0_enable 1 1b Set to 1 to enable OHCI_0

OHCI_1_enable 2 1b Set to 1 to enable OHCI_1