©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 230

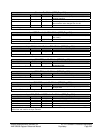

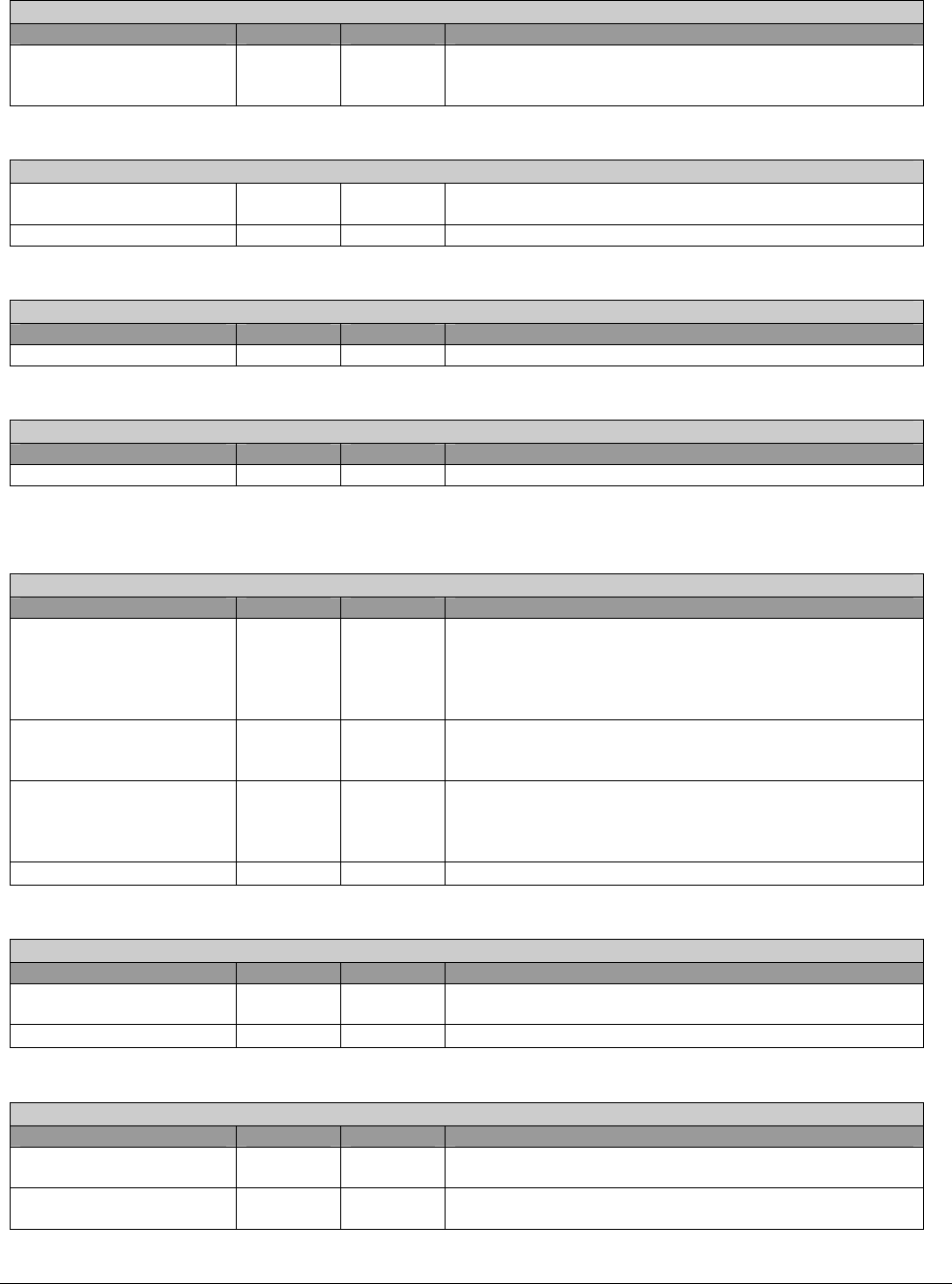

Interrupt Line – RW – 8 bits – [PCI_Reg: 3Ch]

Field Name Bits Default Description

Interrupt Line

7:0 00h This register is used to communicate to software the

interrupt line that the interrupt pin is connected to. It is not

used by the HD Audio controller.

Interrupt Pin – R – 8 bits – [PCI_Reg: 3Dh]

Interrupt Pin 3:0 1h This register reflects the value programs into Interrupt

Control Pin register at offset 44h, bits[3:0]

Reserved 7:4 0h Reserved

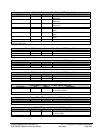

Minimum Grant – R – 8 bits – [PCI_Reg: 3Eh]

Field Name Bits Default Description

Minimum Grant 7:0 00h Hardwired to “0”.

Maximum Latency – R – 8 bits – [PCI_Reg: 3Fh]

Field Name Bits Default Description

Maximum Latency 7:0 00h Hardwired to “0”.

Misc Control Register – RW – 8 bits – [PCI_Reg: 42h]

Field Name Bits Default Description

Disable Non-noop

0 0b 1: Non-snoop attribute is disabled on Buffer Descriptor and

Data Buffer DMA.

0: Set the Non-snoop attribute on Buffer Descriptor and

Data Buffer DMA when the Traffic Priority bit is set in the

Stream Descriptor.

Disable Non-snoop

Override

1 0b 1: Bit[0] of this register controls the Non-snoop attribute

0: override the bit[0] setting meaning always generate No

Snoop attribute on Buffer Descriptor and Data Buffer DMA

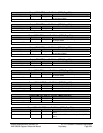

Enable Non-snoop

Request

2 0b 1: Enable Non-snoop request to ACPI

0: Disable Non-snoop request to ACPI

When enabled and the DMA cycle is Non-snoop, ACPI will

not generate a wake to CPU in C2 state.

Reserved

7:3 00h Reserved

Interrupt Pin Control Register – RW – 8 bits – [PCI_Reg: 44h]

Field Name Bits Default Description

Interrupt Pin Control

3:0 1h Controls the value reports in Interrupt Pin Register at offset

0x3D.

Reserved

7:4 0h Reserved

Power Management Capability ID – R – 16 bits – [PCI_Reg: 50h]

Field Name Bits Default Description

Capability ID 7:0 01h Hardwired to 01h. Indicates PCI Power Management

Capability.

Next Capability Pointer 15:8 60h Hardwired to 60h.

Next capability is at offset 60h