©2008 Advanced Micro Devices, Inc.

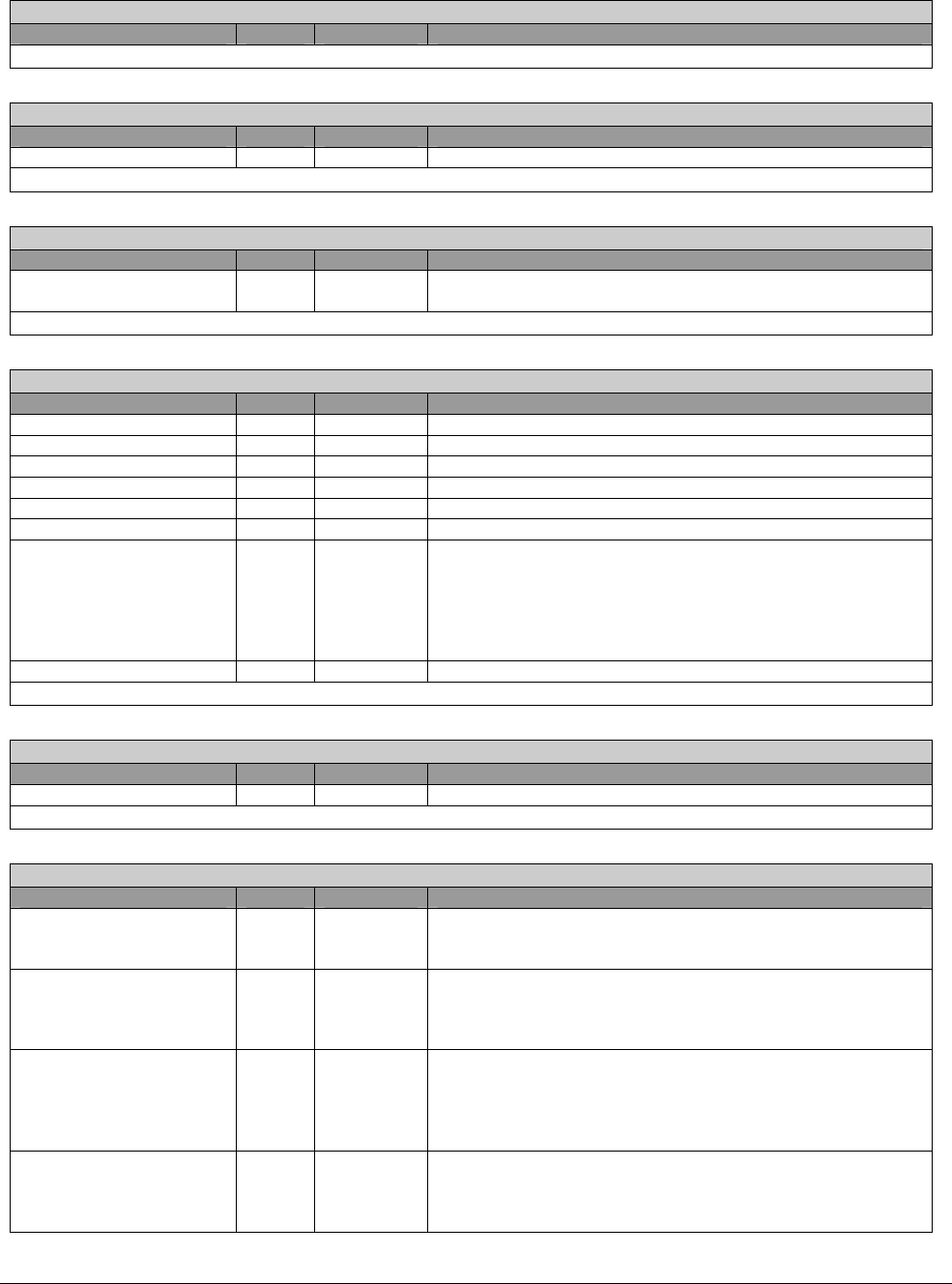

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 169

LdtAgpTimeCntl – RW – 8 bits – [PM_Reg:8Ah]

Field Name Bits Default Description

LdtAgpTimeCntl register for ACPI C state in the K8 system.

StutterTime – RW – 8 bits – [PM_Reg:8Bh]

Field Name Bits Default Description

StutterTime 7:0 00h LDTSTP# duration in 1us increment

StutterTime register for ACPI C state in the K8 system.

StpClkDlyTime – RW – 8 bits – [PM_Reg:8Ch]

Field Name Bits Default Description

StpClkDlyTime 7:0 00h STPCLK# deassertion delay in number of OSC clocks for S1

resume in K8 system.

StpClkDlyTime register for ACPI S state

MiscEnable8D – RW – 8 bits – [PM_Reg:8Dh]

Field Name Bits Default Description

PmeMsgEn 0 0b Set to 1 to enable PmeTurnOff/PmeMsgAck handshake

SlpS2En 1 0b Set to 1 to enable GPM9 as SLP_S2 output

AzRstEn 2 0b Set to 1 to enable GPM8 as AZ_RST# output

DprStpEn 3 0b Set to 1 to enable DPRSTP# output

Ac97PciClkEnB 4 0b Clear to 0 to enable gating of the ac97 internal clock

LongReset 5 0b Set to 1 will cause all reset to be 6ms longer

EffMaskEn 6 0b (Set to 1 for the P4 system and leave it 0 for K8 system).

On the P4 platform, right after the SB exits from the C state,

the LVL read will have no effect until the previous break event

has been cleared. Setting the bit will prevent the SB from

sending the STPCLK# message to the NB during such time.

On the K8 platform the bit has no meaning and must be 0.

Reserved 7 0b

AbPmeCntl register

FakeAsr– RW – 8 bits – [PM_Reg:8Eh]

Field Name Bits Default Description

FakeAsr 7:0 00h Fake alternate status

FakeAsr register

FakeAsrEn– RW – 8 bits – [PM_Reg:8Fh]

Field Name Bits Default Description

FakeAsrEn 0 0b FakeAsr enable. If set, SB will return a fake status (defined in

PMIO_8Eh) when IDE DMA is actively busy and software tries

to read the status from the IDE device

UseBypassRom 1 0b When this bit is set, it will override the ROM straps and use

bits 3:2 of this register to determine which type of ROM to use.

This is for BIOS debugging purpose or for if system desires to

have multiple BIOS on board

BypassRomSel 3:2 00b These two bits will override the two ROM strap pins.

00 – LPC ROM

10 – FWH ROM

11 – SPI ROM

01 – PCI ROM (not used after A13)

BmReqPopUpEn 4 0b When set (along with C state PopUp enabled), BmReq# input

will not cause BM_STS to be set; instead, it will simply act just

like AllowLdtStop and cause the C state machine to pop-up to

C2. This bit is only valid under K8 CPU configuration.