©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual Proprietary Page 265

3.2 Host PCI Bridge Registers (Device 20, Function 4)

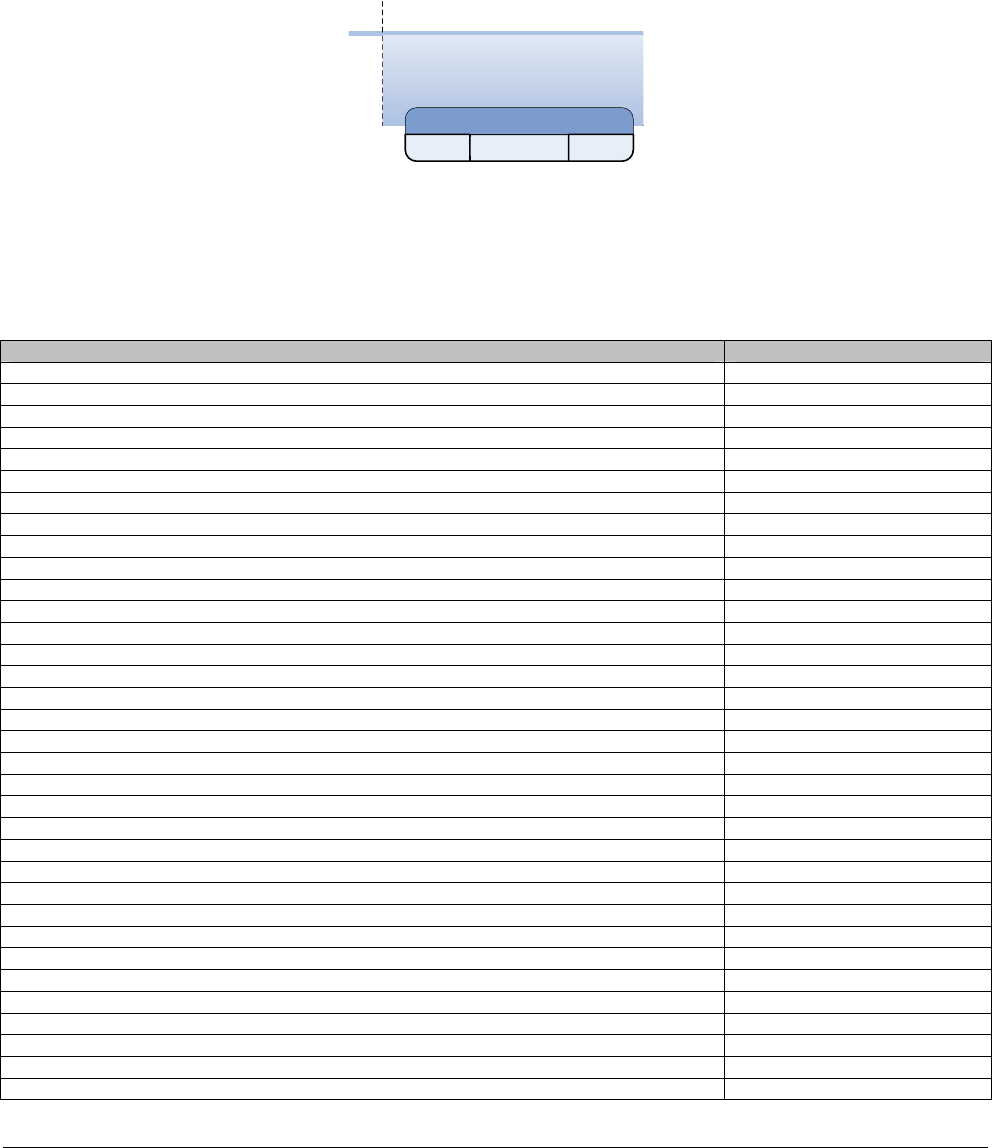

Note: Some PCI functions are controlled by, and associated with, certain PCI configuration registers in the

SMBus/ACPI device. For more information refer to section 2.3: SMBus Module and ACPI Block (Device 20,

Function 0). The diagram below lists these PCI functions and the associated registers.

PCI

PCI Stop Clock enable

PCI Bridge Soft Reset Enable

PCI Bus drive strength registers

C0h

6Ch 64h

PCI_Reg:

PCI Bridge (PCIB) has one set of configuration registers in PCI configuration space identified by PCI function

4 on the South Bridge.

Table 3-1 PCI-to-PCI Bridge Configuration Registers Summary

Register Name Offset Address

Vendor ID 00h

Device ID 02h

PCI Command 04h

PCI Device Status 06h

Revision ID/Class Code 08h

Cache Line Size 0Ch

Latency Timer 0Dh

Header Type 0Eh

Reserved 0Fh

Primary Bus Number 18h

Secondary Bus Number 19h

Subordinate Bus Number 1Ah

Secondary Latency Timer 1Bh

IO Base 1Ch

IO Limit 1Dh

Secondary Status 1Eh

Memory Base 20h

Memory Limit 22h

Prefetchable Memory Base 24h

Prefetchable Memory Limit 26h

IO Base Upper 16 Bits 30h

IO Limit Upper 16 Bits 32h

Capability pointer 34h

Reserved 36h

Interrupt Line 3Ch

Interrupt Pin 3Dh

Bridge Control 3Eh

Chip Control 40h

Diagnostic Control 41h

CLK Control 42h

Arbiter Control and Priority Bits 43h

SMLT Performance 44h

PMLT Performance 46h

PCDMA 48h