©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 29

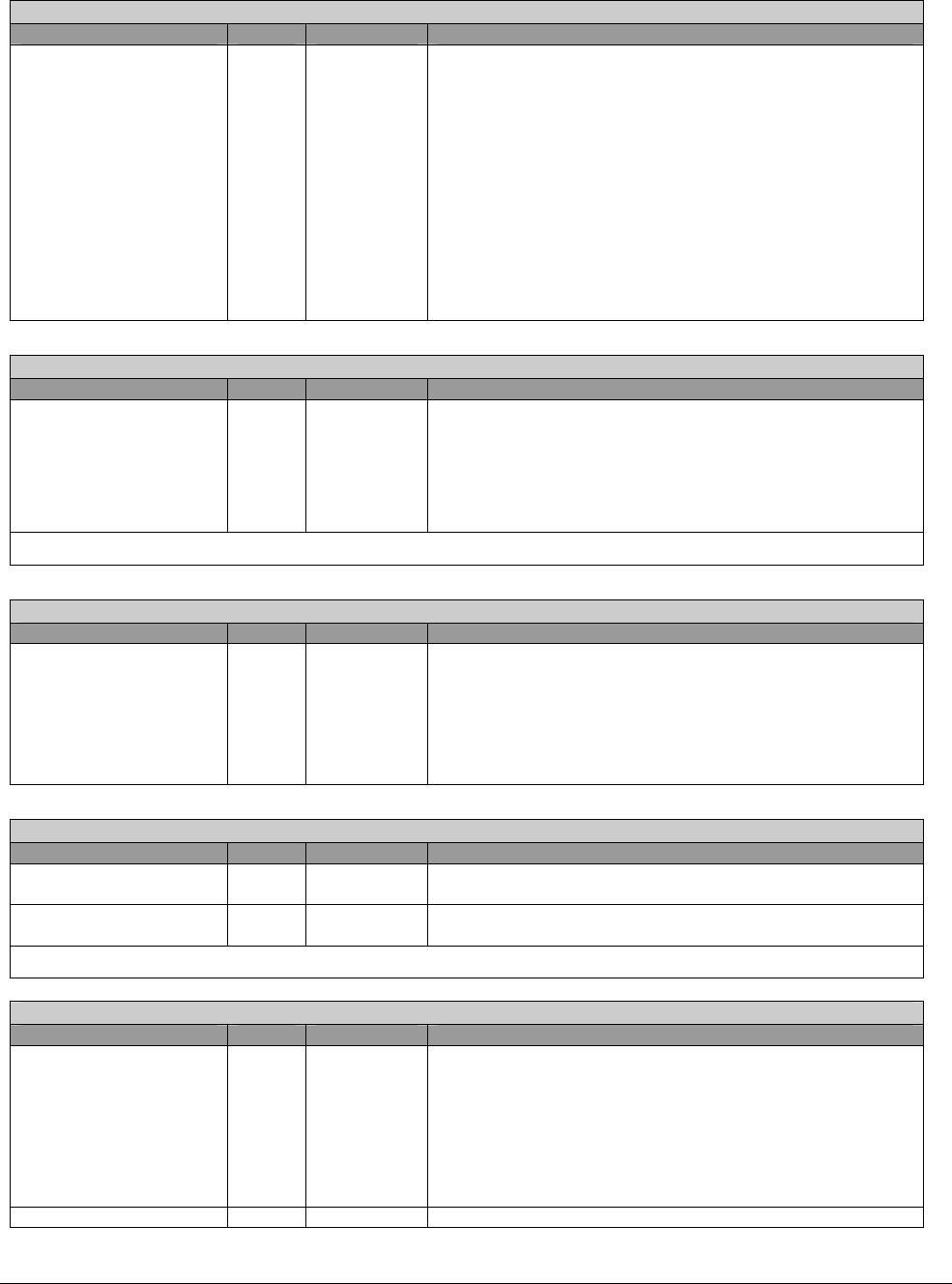

Global HBA Control – RW - 32bits [Mem_reg: ABAR + 04h]

Field Name Bits Default Description

AHCI Enable (AE) 31 0b

When set, indicates that communication to the HBA shall be

via AHCI mechanisms. This can be used by an HBA that

supports both legacy mechanisms (such as SFF-8038i) and

AHCI to know when the HBA is running under an AHCI

driver.

When set, software shall only communicate with the HBA

using AHCI. When cleared, software shall only communicate

with the HBA using legacy mechanisms. When cleared

FISes are not posted to memory and no commands are sent

via AHCI mechanisms.

Software shall set this bit to ‘1’ before accessing other AHCI

registers.

Interrupt Status - RW -32 bits [Mem_reg: ABAR + 08h]

Field Name Bits Default Description

Interrupt Pending Status

(IPS)

31:0 0000_

0000h

If set, indicates that the corresponding port has an interrupt

pending. Software can use this information to determine

which ports require service after an interrupt.

The IPS[x] bit is only defined for ports that are implemented

or for the command completion coalescing interrupt defined

by CCC_CTL.INT. All other bits are reserved.

Write 1 to clear these status bits.

Ports Implemented Register - R -32 bits [Mem_reg: ABAR + 0Ch]

Field Name Bits Default Description

Port Implemented (PI) 31:0 0000000Fh This register is bit significant. If a bit is set to ‘1’, the

corresponding port is available for software to use. If a bit is

cleared to ‘0’, the port is not available for software to use.

The maximum number of bits set to ‘1’ shall not exceed

CAP.NP + 1, although the number of bits set in this register

may be fewer than CAP.NP + 1. At least one bit shall be set

to ‘1’.

AHCI Version- R – 32 bits [Mem_reg: ABAR + 10h]

Field Name Bits Default Description

Minor Version Number

(MNR)

15:0 0100h Indicates the minor version is “10”.

Major Version Number

(MJR)

31:16 0001h Indicates the major version is “1”

Version: V1.10

Command Completion Coalescing Control(CCC_CTL) - RW – 32 bits [Mem_reg: ABAR + 14h]

Field Name Bits Default Description

CCC_CTL Enable 0 0b When cleared to ‘0’, the command completion coalescing

feature is disabled and no CCC interrupts are generated.

When set to ‘1’, the command completion coalescing feature

is enabled and CCC interrupts may be generated based on

timeout or command completion conditions. Software shall

only change the contents of the TV and CC fields when EN is

cleared to ‘0’. On transition of this bit from ‘0’ to ‘1’, any

updated values for the TV and CC fields shall take effect.

Reserved 2:1 Reserved