©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 177

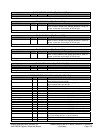

Pm1Enable - RW - 16 bits - [AcpiPmEvtBlk:02h]

Field Name Bits Default Description

Reserved 13:11 000b

PciExpWakeDis 14 1b This bit disables the inputs to the PciExpWakeStatus from

waking the system.

Reserved 15 0b

This register is located at the base address defined by AcpiPmEvtBlk.

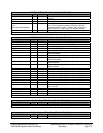

PmControl - RW - 16 bits - [AcpiPm1CntBlk:00h]

Field Name Bits Default Description

SCI_EN 0 0b Selects the power management event to be either an SCI or

SMI# interrupt for the following events. When this bit is set,

then PM events will generate an SCI interrupt; otherwise, it

will be SMI#.

BmRld 1 0b If this bit is set, SCI is raised whenever there is a bus master

active

GBL_RLS 2 0b If PM IO x0E bit[0] is set, writing 1 to this bit will generate

SMI# and set PM IO x0F bit[0]. This bit will always return 0.

Reserved 9:3 00h

SlpType 12:10 000b Defines the sleep state the system enters when the SlpEn is

set to one. This design currently implements 3 states: S1,

S3, and S5

SlpEn 13 0b This is a write-only bit and reads from it always return zero.

If PM_Reg 04h bit7 SLP_SMI_EN is 0, setting this bit causes

the system to sequence into the sleeping state associated

with the SlpType fields programmed. If SLP_SMI_EN is 1,

setting this bit causes SMI#. Writing 0 to this bit has no

effect. This applies to both P4 and K8 systems.

Reserved 15:14 00b

This register is located at the base address defined by AcpiPm1CntBlk.

PmaControl - RW - 8 bits - [AcpiPmaCntBlk:00h]

Field Name Bits Default Description

ARB_DIS 0 0b System arbiter is disabled when this bit is set.

Reserved 7:1 00h

This register is located at the base address defined by AcpiPmaCntBlk.

TmrValue/ETmrValue – R - 32 bits - [AcpiPmTmrBlk:00h]

Field Name Bits Default Description

TmrValue 31:0 - This read-only field returns the running count of the power

management timer.

This register is located at the base address defined by AcpiPmTmrBlk.

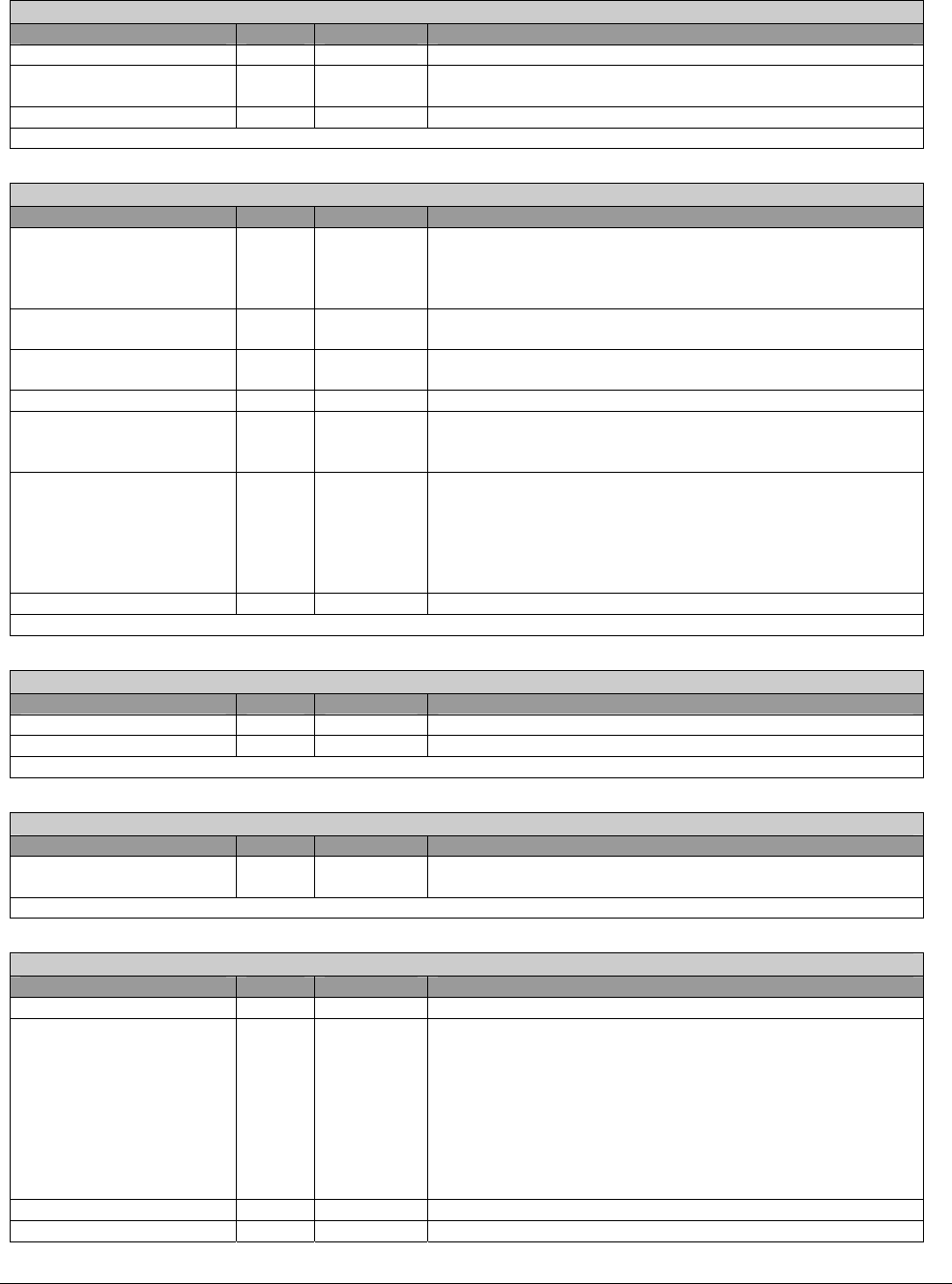

CLKVALUE - RW - 32 bits - [CpuControl:00h]

Field Name Bits Default Description

Reserved 0 0b

ClkValue 3:1 000b These bits define throttle interval for STPCLK# de-assertion

000b: 50%

001b: 12.5%

010b: 25%

011b: 37.5%

100b: 50%

101b: 62.5%

110b: 75%

111b: 87.5%

ThtEn 4 0b This bit enables clock throttling as set in the ClkValue.

Reserved 31:5 0000000h