©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 241

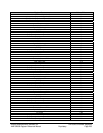

RIRB Response Interrupt Count – RW – 16 bits – [Mem_Reg: Base + 5Ah]

Field Name Bits Default Description

N Response Interrupt

Count

7:0 00h 01h = 1 Response sent to RIRB

:

FFh = 255 Responses sent to RIRB

00h = 256 Responses sent to RIRB

The DMA engine should be stopped when changing this

field or else an interrupt may be lost.

Note that each Response occupies two dwords in the

RIRB.

If more than one codec responds in one frame, then the

count is increased by the number of responses received in

the frame.

Reserved 15:8 00h Reserved. Software must do a read-modify-write to

preserve the value of these bits.

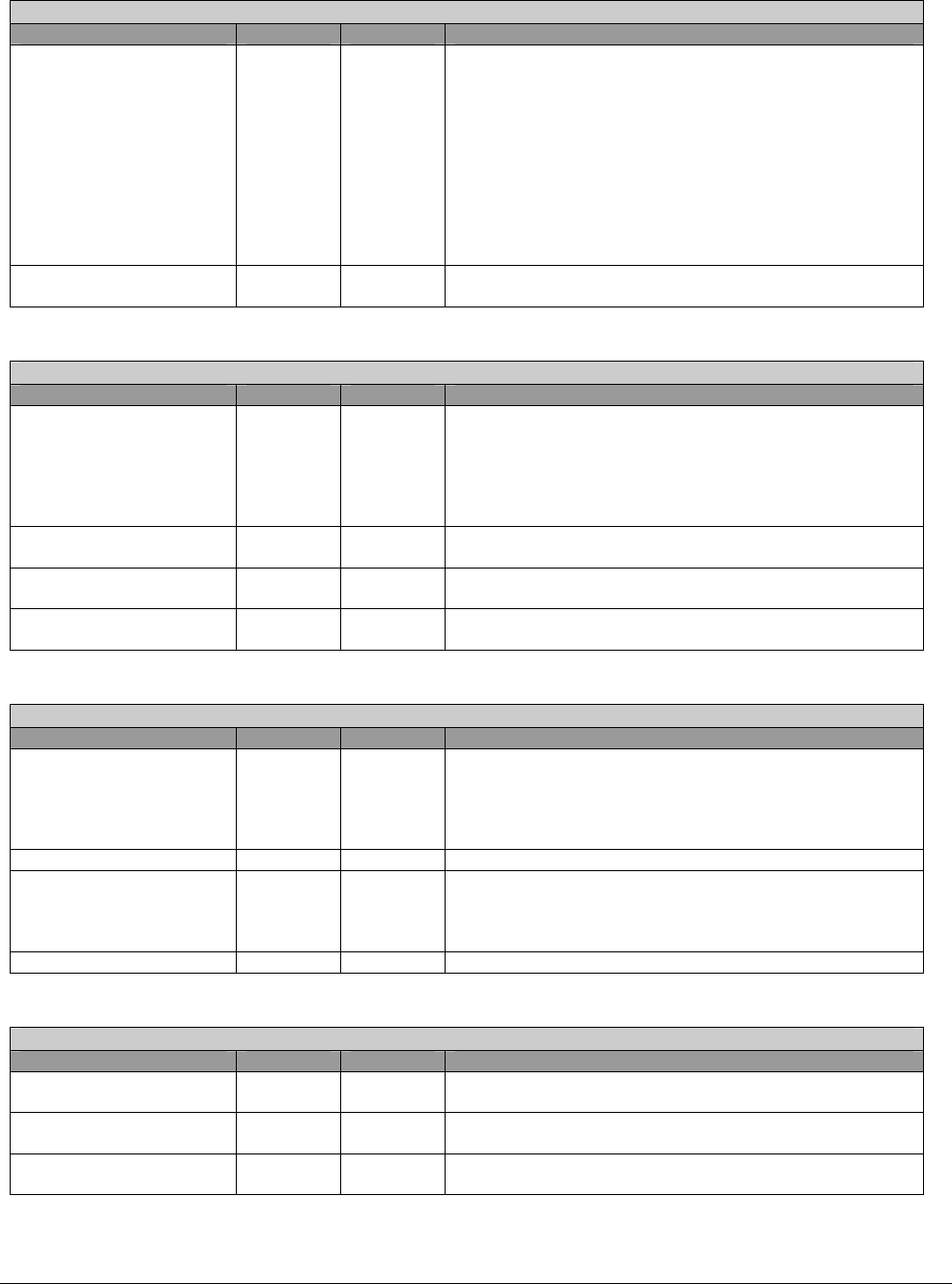

RIRB Control – RW – 8 bits – [Mem_Reg: Base + 5Ch]

Field Name Bits Default Description

Response Interrupt

Control

0 0b 0 = Disable Interrupt

1 = Generate an interrupt after N number of Responses are

sent to the RIRB buffer or when an empty Response slot is

encountered on all SDIN_x inputs after a frame which

return a response (whichever occurs first). The N counter is

reset when the interrupt is generated.

RIRB DMA Enable 1 0b 0 = DMA Stop

1 = DMA Run

Response Overrun

Interrupt Control

2 0b If this bit is set, the hardware will generate an interrupt

when the Response Overrun Interrupt Status is set.

Reserved 7:3 00h Reserved. Software must do a read-modify-write to

preserve the value of these bits.

RIRB Status – RW – 8 bits – [Mem_Reg: Base + 5Dh]

Field Name Bits Default Description

Response Interrupt 0 0b Hardware sets this bit to “1” when an interrupt has been

generated after N number of responses are sent to the

RIRB buffer, or when empty Response slot is encountered

on all SDIN_x inputs (whichever occurs first). Software

clears this bit by writing a “1” to this bit.

Reserved 1 0b Reserved. Software must use 0’s for write to these bits.

Response Overrun

Interrupt Status

2 0b Hardware sets this bit to a “1’ when an overrun occurs in

the RIRB. An interrupt may be generated if the Response

Overrun Interrupt Control bit is set.

Software clears this bit by writing a “1” to it.

Reserved 7:3 0h Reserved. Software must use 0’s for write to these bits.

RIRB Size – RW – 8 bits – [Mem_Reg: Base + 5Eh]

Field Name Bits Default Description

RIRB Size 1:0 10b These bits have no functional impact to the hardware.

This HD Audio controller only supports 256 entries.

Reserved 3:2 0h Reserved. Software must do a read-modify-write to

preserve the value of these bits.

RIRB Size Capability 7:4 4h Hardwired to 4h indicating this controller only supports a

RIRB size of 256 entries.