©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 27

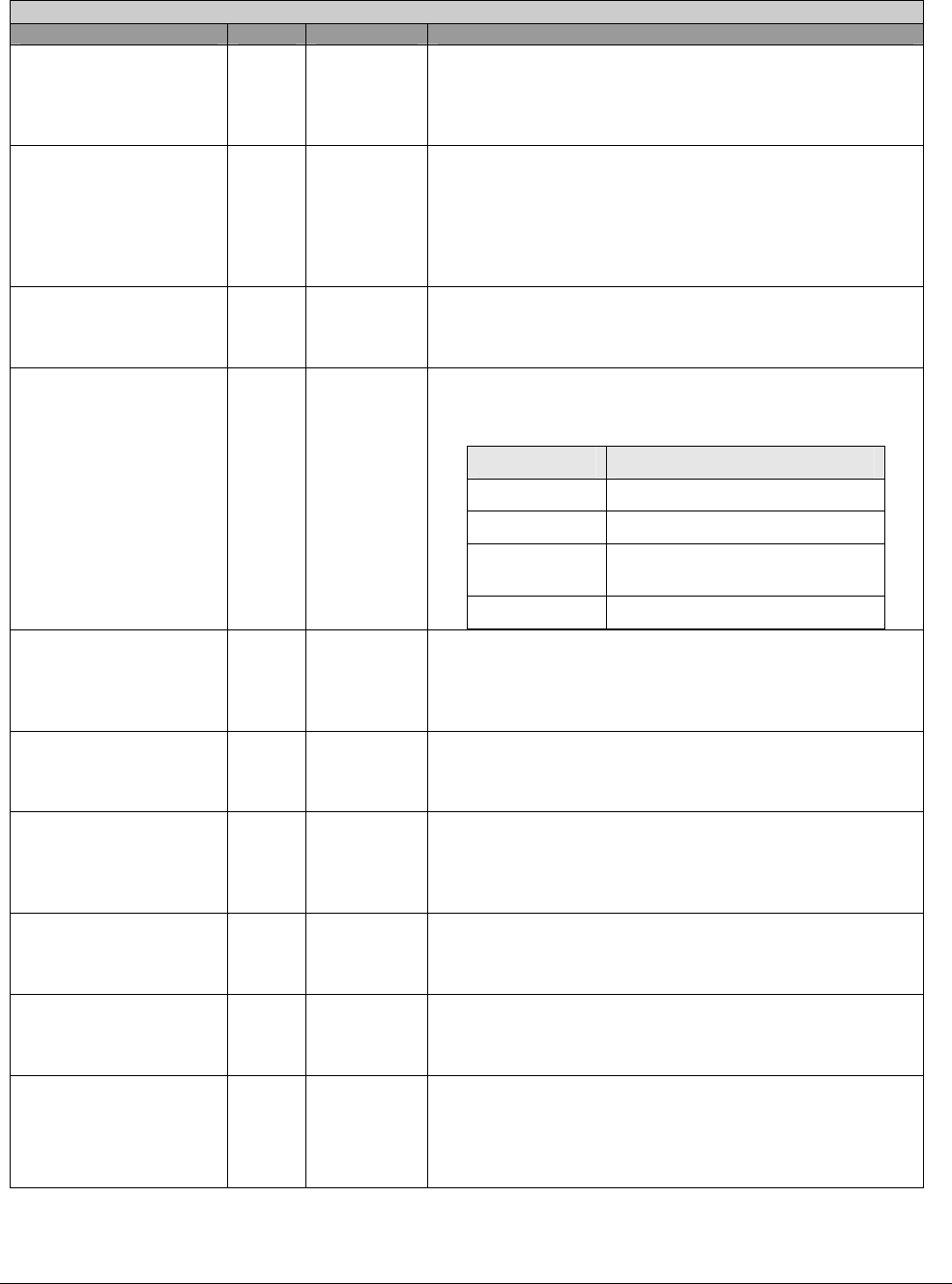

HBA Capabilities – R - 32bits [Mem_reg: ABAR + 00h]

Field Name Bits Default Description

Supports Port Multiplier

(SPM)

17 1b Indicates whether the HBA can support a Port Multiplier.

When set, a Port Multiplier using command-based switching

is supported. When cleared to ‘0’, a Port Multiplier is not

supported, and a Port Multiplier may not be attached to this

HBA.

Supports AHCI mode

only (SAM)

18 0b The SATA controller may optionally support AHCI access

mechanisms only. A value of '0' indicates that in addition to

the native AHCI mechanism (via ABAR), the SATA controller

implements a legacy, task-file based register interface such

as SFF-8038i. A value of '1' indicates that the SATA

controller does not implement a legacy, task-file based

register interface.

Supports Non-Zero DMA

Offsets (SNZO)

19 0b When set to ‘1’, indicates that the HBA can support non-zero

DMA offsets for DMA Setup FISes. This bit is reserved for

future AHCI enhancements. AHCI 1.0 and 1.1 HBAs shall

have this bit cleared to ‘0’.

Interface Speed Support

(ISS)

23:20 2h

Indicates the maximum speed the HBA can support on its

ports. These encodings match the system software

programmable PxSCTL.DET.SPD field. Values are:

Bits Definition

0000 Reserved

0001 Gen 1 (1.5 Gbps)

0010

Gen 1 (1.5 Gbps) and Gen 2 (3

Gbps)

0011 - 1111 Reserved

Supports Command List

Override (SCLO)

24 1b When set to ‘1’, the HBA supports the PxCMD.CLO bit and its

associated function. When cleared to ‘0’, the HBA is not

capable of clearing the BSY and DRQ bits in the Status

register in order to issue a software reset if these bits are still

set from a previous operation.

Supports Activity LED

(SAL)

25 1b When set to ‘1’, the HBA supports a single activity indication

output pin. This pin can be connected to an LED on the

platform to indicate device activity on any drive. When

cleared to ‘0’, this function is not supported.

Supports Aggressive

Link Power Management

(SALP)

26 1b When set to ‘1’, the HBA can support auto-generating link

requests to the Partial or Slumber states when there are no

commands to process. When cleared to ‘0’, this function is

not supported and software shall treat the PxCMD.ALPE and

PxCMD.ASP bits as reserved.

Supports Staggered

Spin-up (SSS)

27 0b When set to ‘1’, the HBA supports staggered spin-up on its

ports, for use in balancing power spikes. When cleared to ‘0’,

this function is not supported. This value is loaded by the

BIOS prior to OS initialization.

Supports Mechanical

Presence Switch (SMPS)

28 1b When set to ‘1’, the HBA supports mechanical presence

switches on its ports for use in hot plug operations. When

cleared to ‘0’, this function is not supported. This value is

loaded by the BIOS prior to OS initialization.

Supports SNotification

Register (SSNTF)

29 1b

When set to ‘1’, the

HBA supports the PxSNTF

(SNotification) register and its associated functionality.

When cleared to ‘0’, the HBA does not support the

PxSNTF (SNotification) register and its associated

functionality.