©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 72

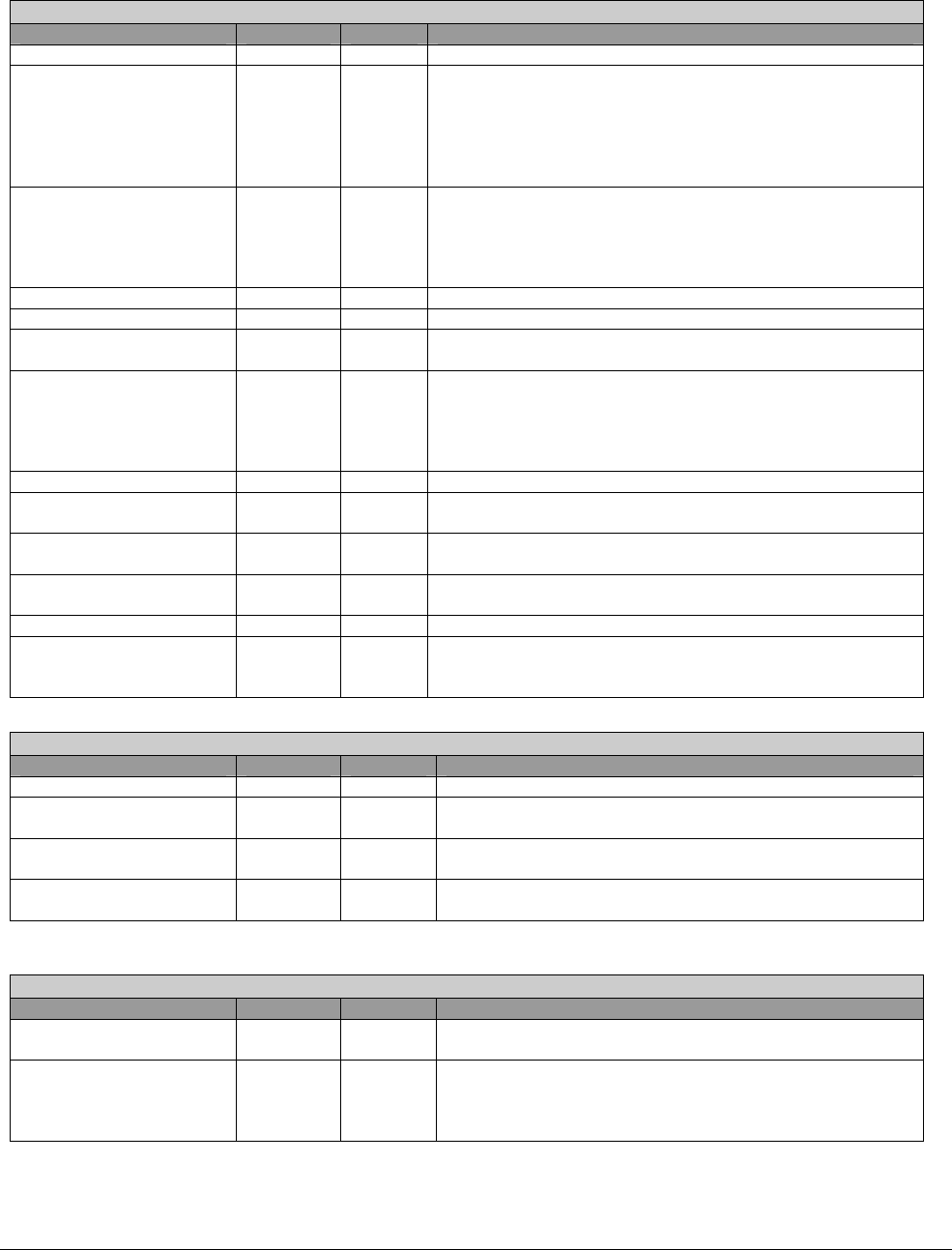

Status – R - 16 bits - [PCI_Reg : 06h]

Field Name Bits Default Description

Reserved 2:0 Reserved

Interrupt Status 3 0b This bit reflects the state of the interrupt in the

device/function. Only when the Interrupt Disable bit in the

command register is a 0 and this Interrupt Status bit is a 1,

will the device’s/function’s INTx# signal be asserted. Setting

the Interrupt Disable bit to a 1 has no effect on the state of

this bit.

Capabilities List 4 1b A value of 0 indicates that no New Capabilities linked list is

available.

A value of 1 indicates that the value read at offset 34h is a

pointer in Configuration Space to a linked list of new

capabilities.

66 MHz Capable 5 1b Hard-wired to 1, indicating 66MHz capable.

Reserved 6 Reserved

Fast Back-to-Back

Capable

7 1b Hard-wired to 1, indicating Fast Back-to-Back capable.

Master Data Parity Error 8 0b This bit is set only when three conditions are met: 1) the bus

agent asserted PERR# itself (on a read) or observed PERR#

asserted (on a write); 2) the agent setting the bit acted as the

bus master for the operation in which the error occurred; and

3) the Parity Error Response bit (Command register) is set.

DEVSEL timing 10:9 01b Hard-wired to 01b – medium timing

Signaled Target Abort 11 0b This bit is set by a target device whenever it terminates a

transaction with Target-Abort.

Received Target Abort 12 0b This bit is set by a master device whenever its transaction is

terminated with Target-Abort.

Received Master Abort 13 0b This bit is set by a master device whenever its transaction

(except for Special Cycle) is terminated with Master-Abort.

Signaled System Error 14 0b This bit is set whenever the device asserts SERR#.

Detected Parity Error 15 0b This bit is set by the device whenever it detects a parity error,

even if parity error handling is disabled (as controlled by bit 6

in the Command register).

Revision ID / Class Code – R - 32 bits - [PCI_Reg : 08h]

Field Name Bits Default Description

Revision ID 7:0 00h Revision ID.

PI 15:8 20h Programming Interface. A constant value of ‘20h’ indentifies

the device being an EHCI Host Controller.

SC 23:16 03h Sub Class. A constant value of ‘03h’ indentifies the device

being of Universal Serial Bus.

BC 31:24 0Ch Base Class. A constant value of ‘0Ch’ identifies the device

being a Serial Bus Controller.

Miscellaneous – RW - 32 bits - [PCI_Reg : 0Ch]

Field Name Bits Default Description

Cache Line Size 7:0 00h This read/write field specifies the system cacheline size in

units of DWORDs and must be initialized to 00h.

Latency Timer 15:8 00h [9:8] hard-wired to 00b, resulting in a timer granularity of at

least four clocks. This field specifies, in units of PCI bus

clocks, the value of the Latency Timer for this PCI bus

master.