©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 51

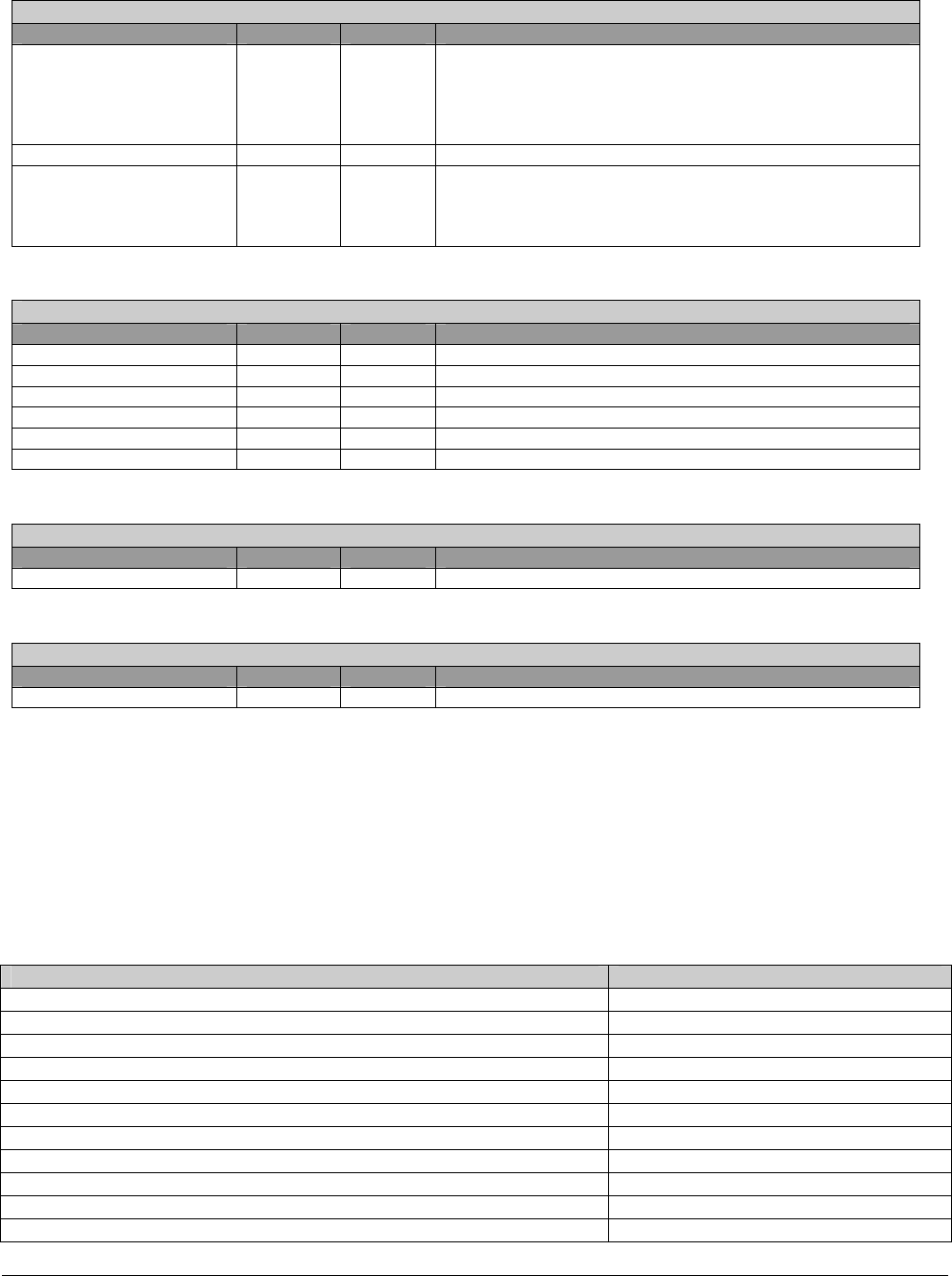

Target Timeout Control (OHCI0 only) – RW - 32 bits - [PCI_Reg : 74h]

Field Name Bits Default Description

Retry counter 7:0 FFh Counter to control the purge of the delay queue when the

host controller does not return the ack. After the counter

expires the transaction is target aborted.

The retry counter can be disabled by writing 00h in this

Register.

Reserved 23:8 0000h Reserved

Timeout Timer 31:24 80h Timer to control the purge of the delay queue when the

master that has initiated the access does not return to

complete the transaction. After the timer expires the queue

is invalidated and the next transaction is serviced.

MSI Control – RW - 32 bits - [PCI_Reg : D0h]

Field Name Bits Default Description

MSI USB 7:0 05h MSI USB ID. Read only.

Next Item Pointer 15:8 00h Pointer to next capability structure

MSI Control Out 16 0b Set to 1 to disable IRQ. Use MSI instead.

Reserved 19:17 0h Reserved

MSI Control 22:20 0h MSI control field

Reserved 31:23 00h Reserved

MSI Address – RW - 32 bits - [PCI_Reg : D4h]

Field Name Bits Default Description

MSI Address 31:0 0h System-specified message address.

MSI Data – RW - 16 bits - [PCI_Reg : D8h]

Field Name Bits Default Description

MSI Data 15:0 0h System-specified message.

2.2.1.2 OHCI Operational Registers (MEM_Reg)

The Host Controller (HC) contains a set of on-chip operational registers, which are mapped into a non-

cacheable portion of the system addressable space. These registers are used by the Host Controller Driver

(HCD) and should be read and written as Dwords.

Reserved bits may be allocated in future releases and should not be assumed to contain 0. The Host

Controller Driver should always preserve the value(s) of the reserved field. When a write to set/clear register

is written, bits written to reserved fields should be 0.

Register Name Offset Address

HcRevision 0h

HcControl 4h

HcCommandStatus 8h

HcInterruptStatus Ch

HcInterruptEnable 10h

HcInterruptDisable 14h

HcHCCA 18h

HcPeriodCurrentED 1Ch

HcControlHeadED 20h

HcControlCurrentED 24h

HcBulkHeadED 28h