©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 31

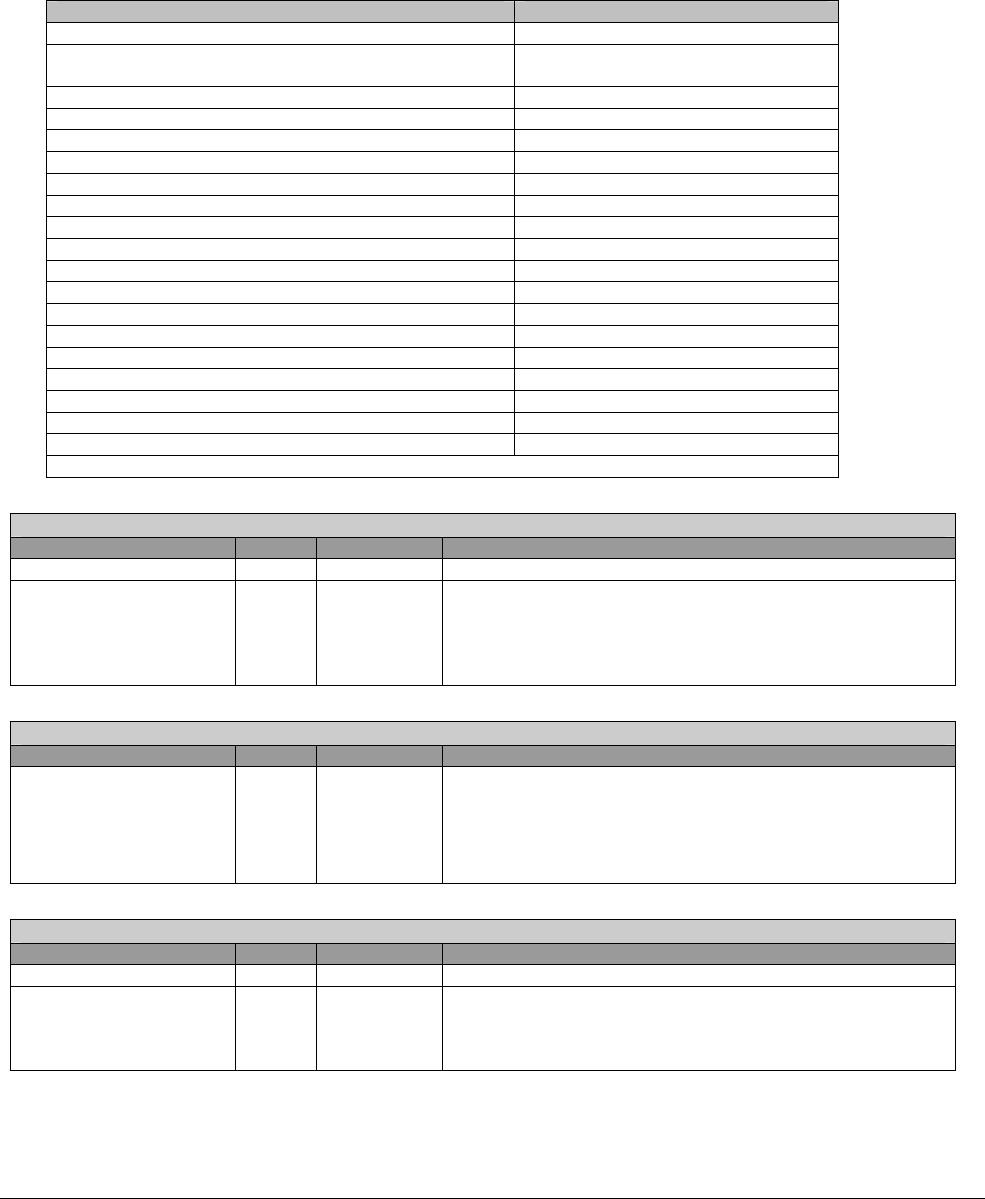

2.1.4.2 Port Registers (One Set Per Port)

The algorithm for the software to determine the offset is as follows:

• Port offset = 100h + (PI Asserted Bit Position * 80h)

Register Name Offset Address

Port-N Command List Base Address(PNCLB) 00h-03h + Port offset

Port-N Command List Base Address Upper 32-

Bits(PNCLBU)

04h-07h + Port offset

Port-N FIS Base Address(PNFB) 08h-0Bh + Port offset

Port-N FIS Base Address Upper 32-Bits(PNFBU) 0Ch-0Fh + Port offset

Port-N Interrupt Status(PNIS) 10h-13h + Port offset

Port-N Interrupt Enable(PNIE) 14h-17h + Port offset

Port-N Command and Status(PNCMD) 18h-1Bh + Port offset

Reserved 1Ch-1Fh + Port offset

Port-N Task File Data(PNTFD) 20h-23h + Port offset

Port-N Signature(PNSIG) 24h-27h + Port offset

Port-N Serial ATA Status (PNSSTS) 28h-2Bh + Port offset

Port-N Serial ATA Control (PNSCTL) 2Ch-2Fh + Port offset

Port-N Serial ATA Error (PNSERR) 30h-33h + Port offset

Port-N Serial ATA Active (PNSACT) 34h-37h + Port offset

Port-N Command Issue(PNCI) 38h-3Bh + Port offset

Port-N SNotification (PNSNTF) 3Ch-3Fh + Port offset

Reserved for FIS-based Switching Definition 40h-43h + Port offset

Reserved 44h-6Fh + Port offset

Port-N Vendor Specific(PNVS) 70h-7Fh + Port offset

*N is the port number, 0 ~ 3

Port-N Command List Base Address -RW -32 bits [Mem_reg: ABAR + port offset + 00h]

Field Name Bits Default Description

Reserved 9:0 Reserved.

Command List Base

Address (CLB)

31:10 000000h Indicates the 32-bit base physical address for the command

list for this port. This base is used when fetching commands

to execute. The structure pointed to by this address range is

1K-bytes in length. This address must be 1K-byte aligned as

indicated by bits 09:00 being read only.

Port-N Command List Base Upper Address -RW - 32 bits [Mem_reg: ABAR + port offset + 04h]

Field Name Bits Default Description

Command List Base

Address Upper (CLBU)

31:0 00000000h

Indicates the upper 32-bits for the command list base

physical address for this port. This base is used when

fetching commands to execute.

This register shall be read only ‘0’ for HBAs that do not

support 64-bit addressing.

Port–N FIS Base Address -RW -32 bits [Mem_reg: ABAR + port offset + 08h]

Field Name Bits Default Description

Reserved 7:0 Reserved.

FIS Base Address (FB) 31:8 000000h Indicates the 32-bit base physical address for received FISes.

The structure pointed to by this address range is 256 bytes in

length. This address must be 256-byte aligned as indicated

by bits 07:00 being read only.