©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 237

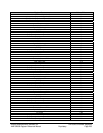

Input Stream Payload Capability – R – 16 bits - [Mem_Reg: Base + 1Ah]

Field Name Bits Default Description

Input Stream Payload

Capability

15:0 0000h This field indicates the maximum number of words per

frame for any single input stream. This measurement is in

16-bit word quantities per 48 kHz frame. The value must

not be greater than the Input Payload Capability register

value. Software must ensure that a format which would

cause more words per frame than indicated is not

programmed into the Input Stream Descriptor register.

00h: No Limit ( Stream size is limited only by Input Payload

Capability register)

01h: 1 word payload

:

:

FFh: 255 word payload

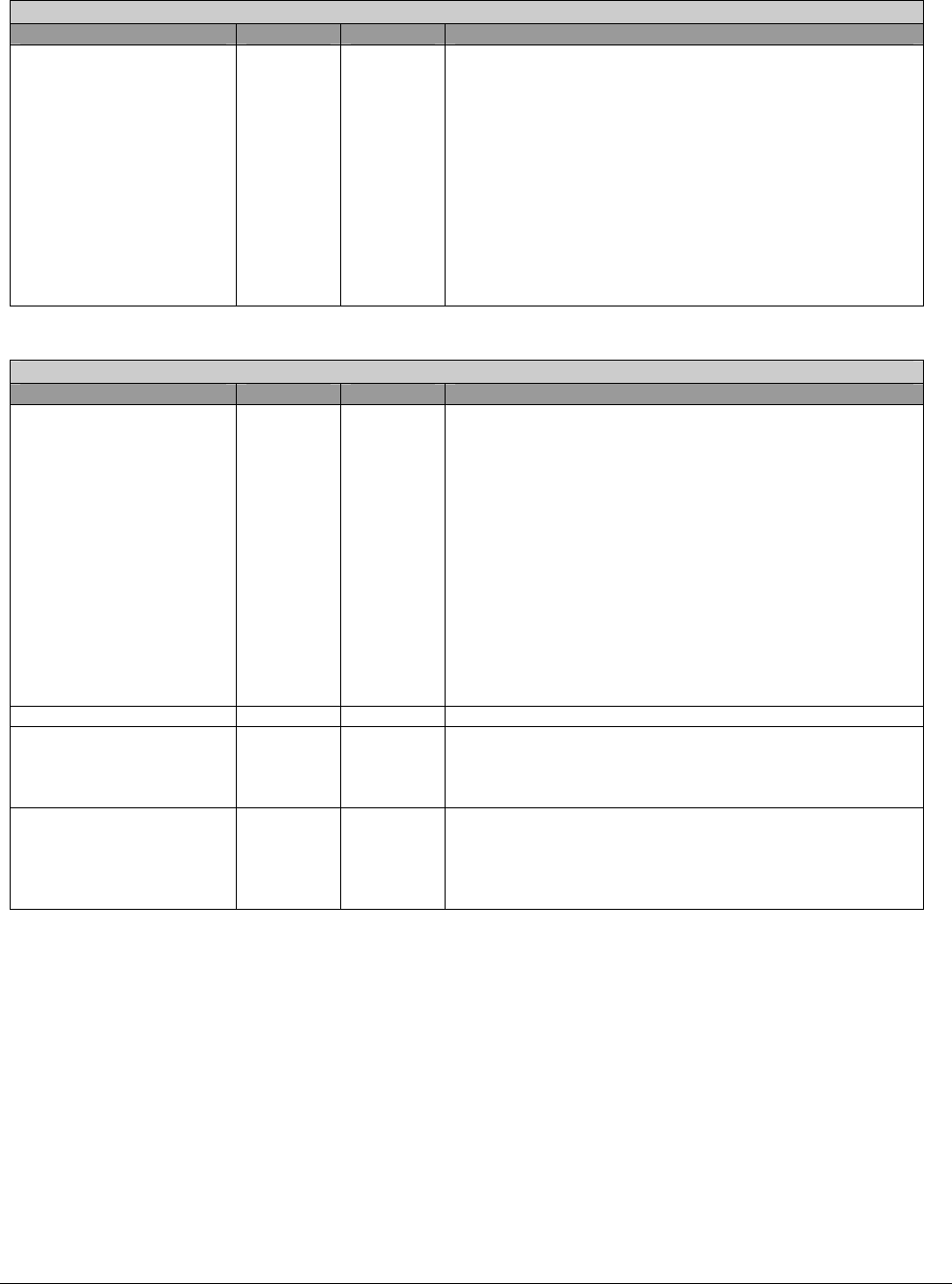

Interrupt Control – RW – 32 bits - [Mem_Reg: Base + 20h]

Field Name Bits Default Description

Stream Interrupt Enable 7:0 00h When set to “1”, the individual streams are enabled to

generate an interrupt when the corresponding stream

status bits are set.

A stream interrupt is caused as a result of a buffer with IOC

in the BDL entry being completed or as result of FIFO

error. Control over the generation of each of these sources

is in the associated Stream Descriptor.

Bit[0]: Input Stream 0

Bit[1]: Input Stream 1

Bit[2]: Input Stream 2

Bit[3]: Input Stream 3

Bit[4]: Output Stream 0

Bit[5]: Output Stream 1

Bit[6]: Output Stream 2

Bit[7]: Output Stream 3

Reserved 29:8 000000h Reserved

Controller Interrupt Enable 30 0b Enables the general interrupt for controller functions. When

set to “1’, the controller generates an interrupt when the

corresponding status bit gets set due to a Response

Interrupt, a Response Buffer Overrun, and Wake events.

Global Interrupt Enable 31 0b Enables device interrupt generation. When set to “1”, the

HD Audio device is enabled to generate an interrupt. This

control is in addition to any bits in the bus specific address

space such as the Interrupt Enable bit in the PCI

Configuration Space.