©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 89

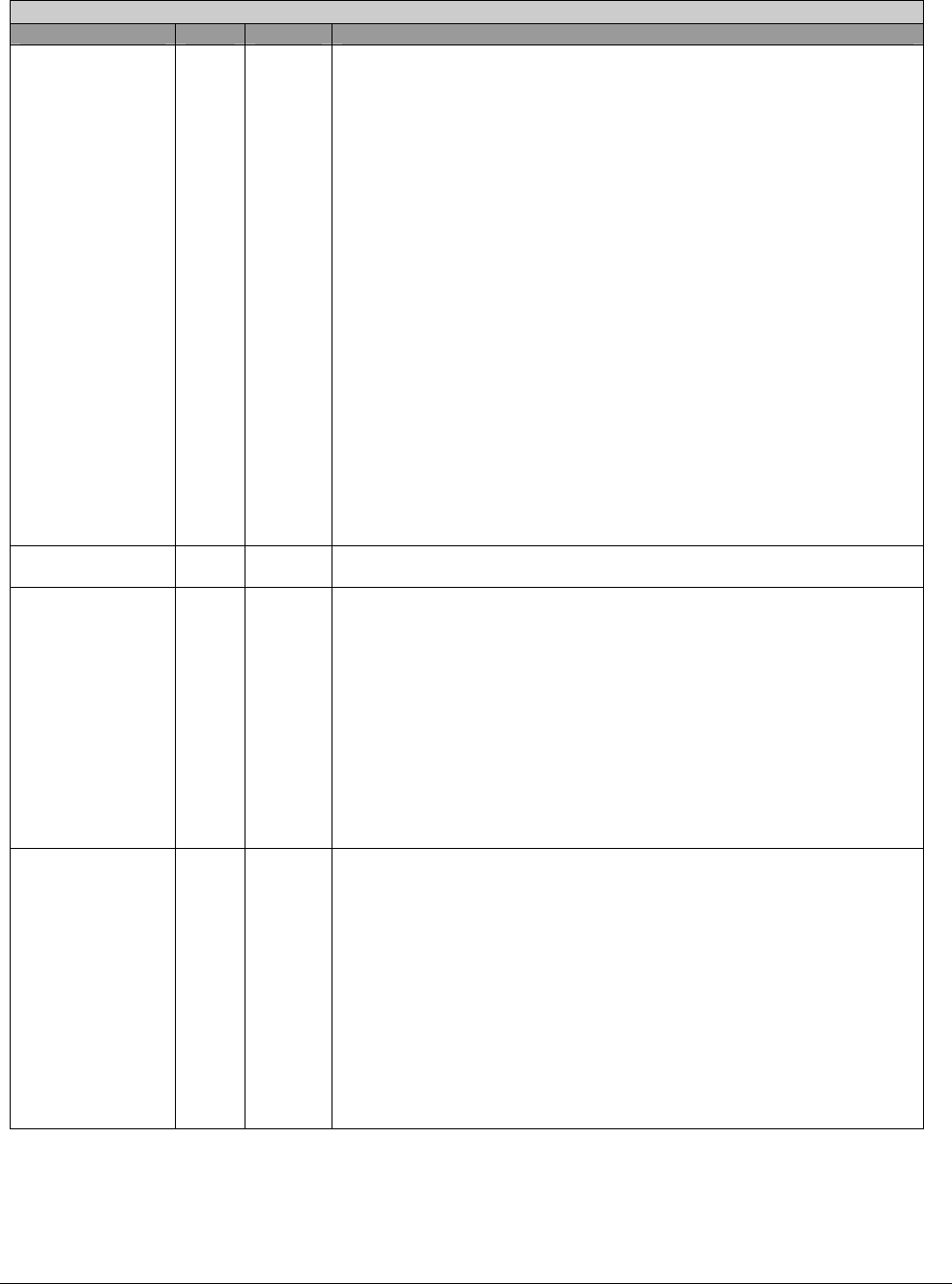

PORTSC (1-N_PORTS) –RW - 32 bits - [EOR_Reg : EHCI_EOR + (44h~68h)]

Field Name Bits Default Description

Port Reset 8 0b 1 = Port is in Reset.

0 = Port is not in Reset.

When software writes a one to this bit (from a zero), the bus reset

sequence as defined in the USB Specification Revision 2.0 is started.

Software writes a zero to this bit to terminate the bus reset sequence.

Software must keep this bit at a one long enough to ensure the reset

sequence, as specified in the USB Specification Revision 2.0, completes.

Note: when software writes this bit to a one, it must also write a zero to

the Port Enable bit.

Note that when software writes a zero to this bit there may be a delay

before the bit status changes to a zero. The bit status will not read as a

zero until after the reset has completed. If the port is in high-speed mode

after reset is complete, the host controller will automatically enable this

port (e.g. set the Port Enable bit to a one). A host controller must

terminate the reset and stabilize the state of the port within 2 milliseconds

of software transitioning this bit from a one to a zero. For example: if the

port detects that the attached device is high-speed during reset, then the

host controller must have the port in the enabled state within 2ms of

software writing this bit to a zero.

The HCHalted bit in the USBSTS register should be a zero before

software attempts to use this bit. The host controller may hold Port Reset

asserted to a one when the

HCHalted bit is a one. This field is zero if Port Power is zero.

Reserved 9 This bit is reserved for future use, and should return a value of zero when

read.

Line Status 11:10 These bits reflect the current logical levels of the D+ (bit 11) and D-

(bit 10) signal lines. These bits are used for detection of low-speed USB

devices prior to the port reset and enable sequence. This field is valid

only when the port enable bit is zero and the current connect status bit is

set to a one.

The encoding of the bits are:

Bits[11:10] USB State Interpretation

00b SE0 Not Low-speed device, perform EHCI reset

10b J-state Not Low-speed device, perform EHCI reset

01b K-state Low-speed device, release ownership of port

11b Undefined Not Low-speed device, perform EHCI reset.

This value of this field is undefined if Port Power is zero.

[Read-only]

Port Power 12 The function of this bit depends on the value of the Port Power Control

(PPC) field in the HCSPARAMS register. The behavior is as follows:

PPC PP Operation

0b 1b RO - Host controller does not have port power control

switches. Each port is hard-wired to power.

1b 1b/0b RW - Host controller has port power control switches.

This bit represents the current setting of the switch (0 = off, 1 = on). When

power is not available on a port (i.e.

PP equals a 0), the port is non-functional and will not report attaches,

detaches, etc.

When an over-current condition is detected on a powered port and PPC is

a one, the PP bit in each affected port may be transitioned by the host

controller from a 1 to 0 (removing power from the port).

[Read-write or Read-only]