©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 139

2.3.3.1.3 System Reset Register (IO CF9)

Note: Refer to PM IO reg x85 for a detailed description. This register has been designed to be dual-port

accessible.

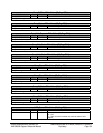

2.3.3.2 Power Management (PM) Registers

The power management (PM) block is resident in the PCI/LPC/ISA bridge. The PM registers are accessed

via IO mapped registers xCD6h and xCD7h. The index address is first programmed into IO register xCD6h.

Read or write values are accessed through IO register xCD7h.

Register Name Offset Address

MiscControl 00h

MiscStatus 01h

SmiWakeUpEventEnable1 02h

SmiWakeUpEventEnable2 03h

SmiWakeUpEventEnable3 04h

SmiWakeUpEventStatus1 05h

SmiWakeUpEventStatus2 06h

SmiWakeUpEventStatus3 07h

InactiveTmrEventEnable1 08h

InactiveTmrEventEnable2 09h

InactiveTmrEventEnable3 0Ah

PmTmr1InitValue 0Bh

PmTmr1CurValue 0Ch

PwrLedExtEvent 0Dh

PwrLedExtEvent 0Eh

AcpiStatus 0Fh

AcpiEn 10h

S1AgpStpEn 11h

PmTmr2InitValue 12h

PmTmr2CurValue 13h

Programlo0RangeLo 14h

Programlo0RangeHi 15h

ProgramIo1RangeLo 16h

ProgramIo1RangeHi 17h

ProgramIo2RangeLo 18h

ProgramIo2RangeHi 19h

ProgramIo3RangeLo 1Ah

ProgramIo3RangeHi 1Bh

ProgramIoEnable 1Ch

IOMonitorStatus 1Dh

InactiveTmrEventEnable4 1Eh

AcpiPm1EvtBlkLo 20h

AcpiPm1EvtBlkHi 21h

AcpiPm1CntBlkLo 22h

AcpiPm1CntBlkHi 23h

AcpiPmTmrBlkLo 24h

AcpiPmTmrBlkHi 25h

CpuControlLo 26h

CpuControlHi 27h

AcpiGpe0BlkLo 28h

AcpiGpe0BlkHi 29h

AcpiSmiCmdLo 2Ah

AcpiSmiCmdHi 2Bh