©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 235

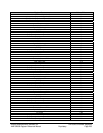

Output Payload Capability – R – 16 bits - [Mem_Reg: Base + 04h]

Field Name Bits Default Description

Output Payload Capability 15:0 003Ch Hardwired to 3Ch. Indicates the total output payload on the

link. This does not include bandwidth used for command

and control. This measurement is in 16-bit word quantities

per 48kHz frame. The default link clock speed of 24MHz

(double data rate) provides 1000 bits per frame minus 40

bits for command and control, leaving 960 bits (60 words)

for data payload.

Input Payload Capability – R – 16 bits - [Mem_Reg: Base + 06h]

Field Name Bits Default Description

Input Payload Capability 15:0 001Dh Hardwired to 1Dh. Indicates the total input payload on the

link. This does not include bandwidth used for response.

This measurement is in 16-bit word quantities per 48kHz

frame. The default link clock speed of 24MHz provides 500

bits per frame minus 36 bits for response, leaving 464 bits

(29 words) for data payload.

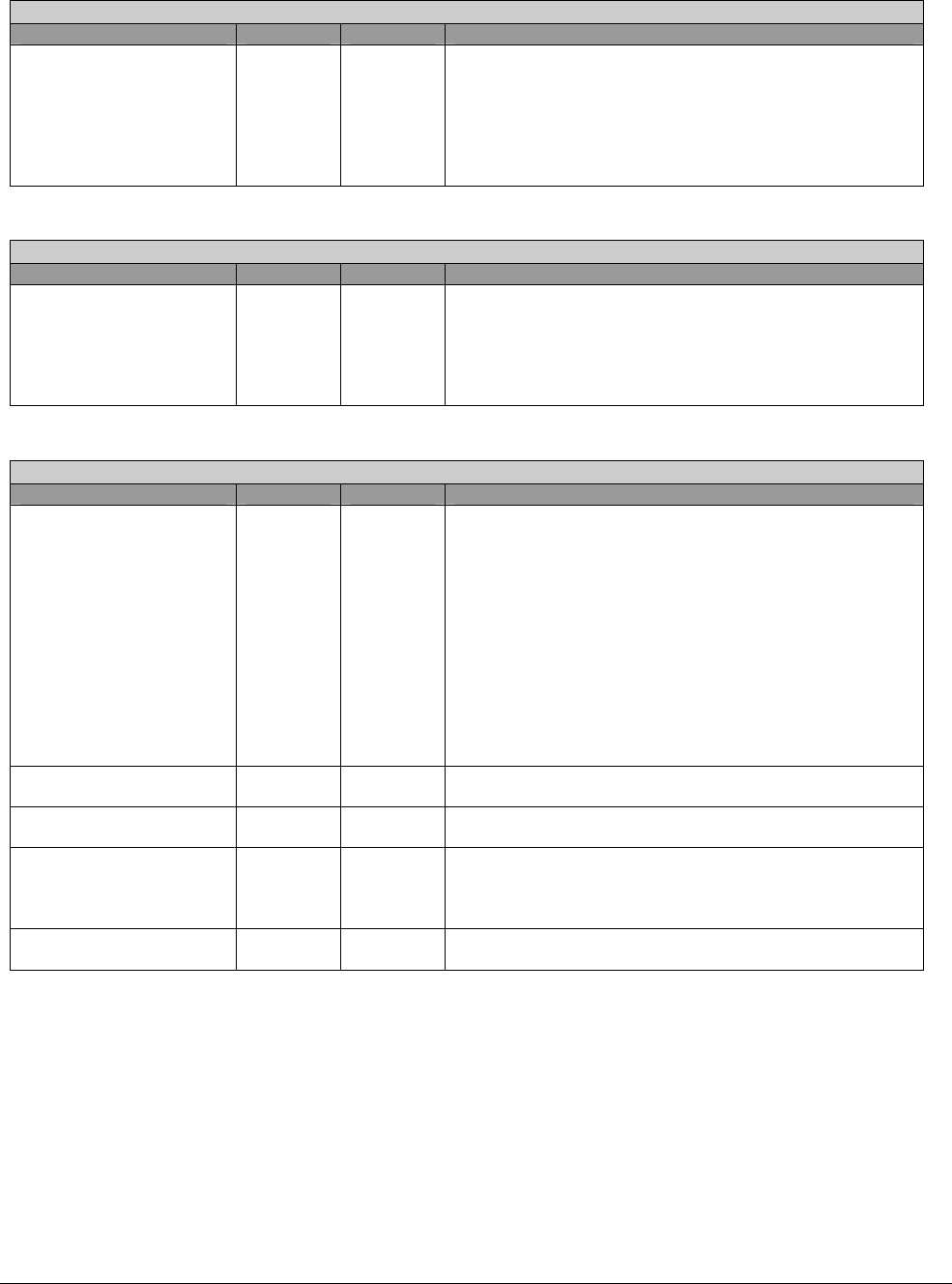

Global Control – RW – 32 bits - [Mem_Reg: Base + 08h]

Field Name Bits Default Description

Controller Reset 0 0b Writing a 0 to this bit causes the controller to transition to

the Reset state. After the hardware has completed

sequencing into the Reset state, it will report a 0 in this bit.

Software must read a 0 from this bit to verify that the

controller is in reset.

Writing a “1” to this bit causes the controller to exit the

Reset state and deassert the link RESET# signals.

Software is responsible for setting/clearing this bit such that

the minimum link RESET# signal assertion pulse width

specification is met.

When the controller hardware is ready to begin operation, it

will report a “1” in this bit. Software must read a 1 from this

bit before accessing any controller registers.

Flush Control 1 0b Writing a 1 to this bit initiates a flush. The flush is

completed when Flush Status is set.

Reserved 7:2 00h Reserved. Software must do a read-modify-write to

preserve the value of these bits.

Accepted Unsolicited

Response Enable

8 0b If “1”, Unsolicited Response from the codecs are accepted

by the controller and placed into the Response Input Ring

Buffer. If “0”, Unsolicited Responses are accepted and

dropped.

Reserved 31:9 000000h Reserved. Software must do a read-modify-write to

preserve the value of these bits.