©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual Proprietary Page 224

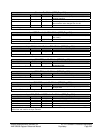

Output DMA2 DT Start– R - 32 bits - [MEM_Reg: 50h]

Field Name Bits Default Description

out DMA2 DT start 31:0 0000_0000h Pointer to the start of data associated with current DT

for the Output DMA2.

Output DMA2 Discrete Table (DT) Start Pointer Register:

Output DMA2 DT Next– R - 32 bits - [MEM_Reg: 54h]

Field Name Bits Default Description

out DMA2 DT next 31:0 0000_0000h Pointer to the next DT for the Output DMA2

Output DMA2 DT Next Pointer Register:

Output DMA2 DT Current– R - 32 bits - [MEM_Reg: 58h]

Field Name Bits Default Description

out DMA2 DT current 31:0 0000_0000h Pointer to the currently accessing memory address for

the Output DMA2.

Output DMA2 DT Current Pointer Register:

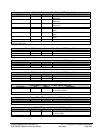

Output DMA3 DT Start– R - 32 bits - [MEM_Reg: 5Ch]

Field Name Bits Default Description

out DMA3 DT start 31:0 0000_0000h Pointer to the start of data associated with current DT

for the Output DMA3.

Output DMA3 Discrete Table (DT) Start Pointer Register:

Output DMA3 DT Next– R - 32 bits - [MEM_Reg: 60h]

Field Name Bits Default Description

out DMA3 DT next 31:0 0000_0000h Pointer to the next DT for the Output DMA3

Output DMA3 DT Next Pointer Register:

Output DMA3 DT Current– R - 32 bits - [MEM_Reg: 64h]

Field Name Bits Default Description

out DMA3 DT current 31:0 0000_0000h Pointer to the currently accessing memory address for

the Output DMA3.

Output DMA3 DT Current Pointer Register:

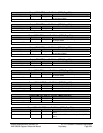

Output DMA 1/2 DT Size– R - 32 bits - [MEM_Reg: 68h]

Field Name Bits Default Description

out DMA 1 DT size 15:0 0000h Data size of DT for Output DMA # 1.

out DMA 2 DT size 31:16 0000h Data size of DT for Output DMA # 2.

Output DMA 1/2 DT Size Register:

Output DMA 3 DT Size– R - 32 bits - [MEM_Reg: 6Ch]

Field Name Bits Default Description

out DMA 1 DT size 15:0 0000h Data size of DT for Output DMA # 1.

Reserved 31:16 0000h

Output DMA 3 DT Size Register:

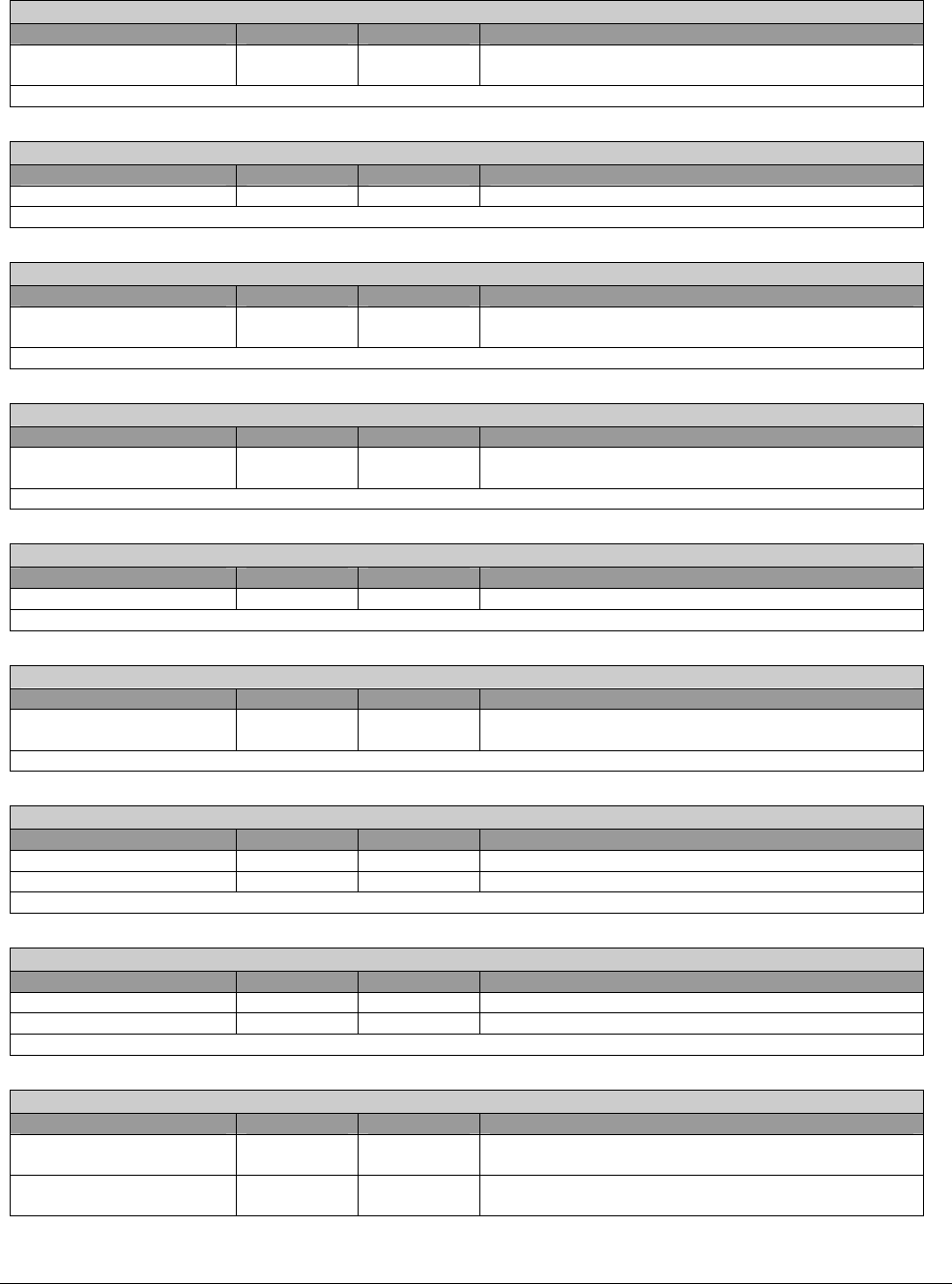

Output DMA 1/2/3 FIFO Info– R - 32 bits - [MEM_Reg: 70h]

Field Name Bits Default Description

out DMA1 Used 4:0 00h Number of filled FIFO entries of Output DMA1 (FIFO

size 6).

out DMA2 Used 9:5 00h Number of filled FIFO entries of Output DAM2 (FIFO

size 6).