©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 86

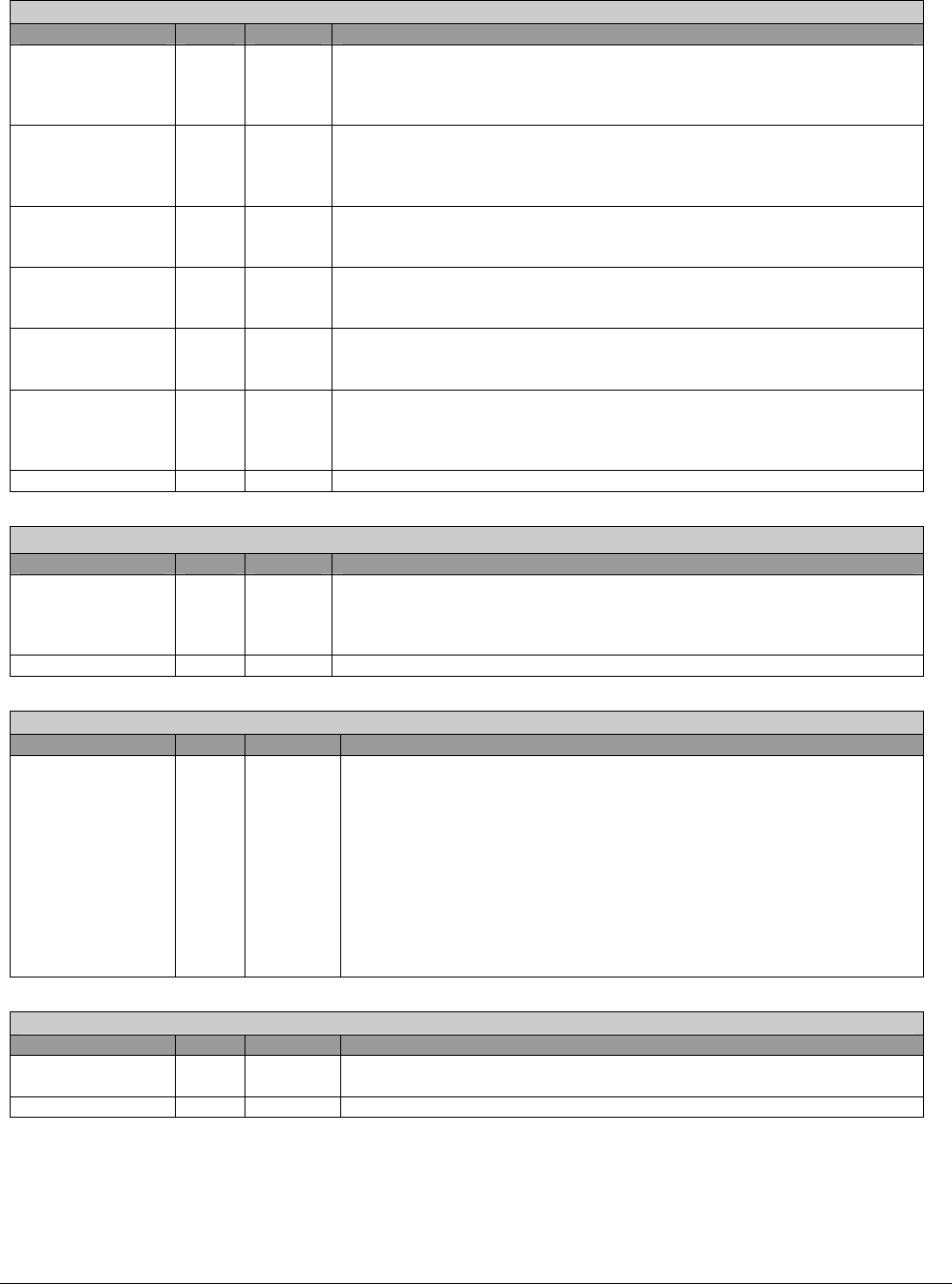

USBINTR –RW - 32 bits - [EOR_Reg : EHCI_EOR + 08h]

Field Name Bits Default Description

USB Interrupt

Enable

0 0b When this bit is a one, and the USBINT bit in the USBSTS register is a

one, the host controller will issue an interrupt at the next interrupt

threshold. The interrupt is acknowledged by software clearing the

USBINT bit.

USB Error

Interrupt Enable

1 0b When this bit is a one, and the USBERRINT bit in the USBSTS register is

a one, the host controller will issue an interrupt at the next interrupt

threshold. The interrupt is acknowledged by software clearing the

USBERRINT bit.

Port Change

Interrupt Enable

2 0b When this bit is a one, and the Port Change Detect bit in the USBSTS

register is a one, the host controller will issue an interrupt. The interrupt is

acknowledged by software clearing the Port Change Detect bit.

Frame List

Rollover Enable

3 0b When this bit is a one, and the Frame List Rollover bit in the USBSTS

register is a one, the host controller will issue an interrupt. The interrupt is

acknowledged by software clearing the Frame List Rollover bit.

Host System Error

Enable

4 0b When this bit is a one, and the Host System Error Status bit in the

USBSTS register is a one, the host controller will issue an interrupt. The

interrupt is acknowledged by software clearing the Host System Error bit.

Interrupt on Async

Advance Enable

5 0b When this bit is a one, and the Interrupt on Async Advance bit in the

USBSTS register is a one, the host controller will issue an interrupt at the

next interrupt threshold. The interrupt is acknowledged by software

clearing the Interrupt on Async Advance bit.

Reserved 31:6 These bits are reserved and should be zero

FRINDEX –RW - 32 bits - [EOR_Reg : EHCI_EOR + 0Ch]

Field Name Bits Default Description

Frame Index 13:0 0h When this bit is a one, and the Interrupt on Async Advance bit in the

USBSTS register is a one, the host controller will issue an interrupt at the

next interrupt threshold. The interrupt is acknowledged by software

clearing the Interrupt on Async Advance bit.

Reserved 31:14 These bits are reserved and should be zero

CTRLDSSEGMENT –RW - 32 bits - [EOR_Reg : EHCI_EOR + 10h]

Field Name Bits Default Description

CTRLDSSEGME

NT

31:0 0h This 32-bit register corresponds to the most significant address bits

[63:32] for all EHCI data structures. If the 64-bit Addressing Capability

field in HCCPARAMS is a zero, then this register is not used. Software

cannot write to it and a read from this register will return zeros.

If the 64-bit Addressing Capability

field in HCCPARAMS is a one, then

this register is used with the link pointers to construct 64-bit addresses to

EHCI control data structures. This register is concatenated with the

link pointer from either the PERIODICLISTBASE, ASYNCLISTADDR, or

any control data structure link field to construct a 64-bit address.

This register allows the host software to locate all control data structures

within the same 4 Gigabyte memory segment.

PERIODICLISTBASE –RW - 32 bits - [EOR_Reg : EHCI_EOR + 14h]

Field Name Bits Default Description

Reserved 11:0 These bits are reserved. Must be written as 0s. During runtime, the

values of these bits are undefined.

Base Address 31:12 000h These bits correspond to memory address signals [31:12], respectively.