©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 132

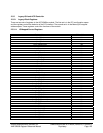

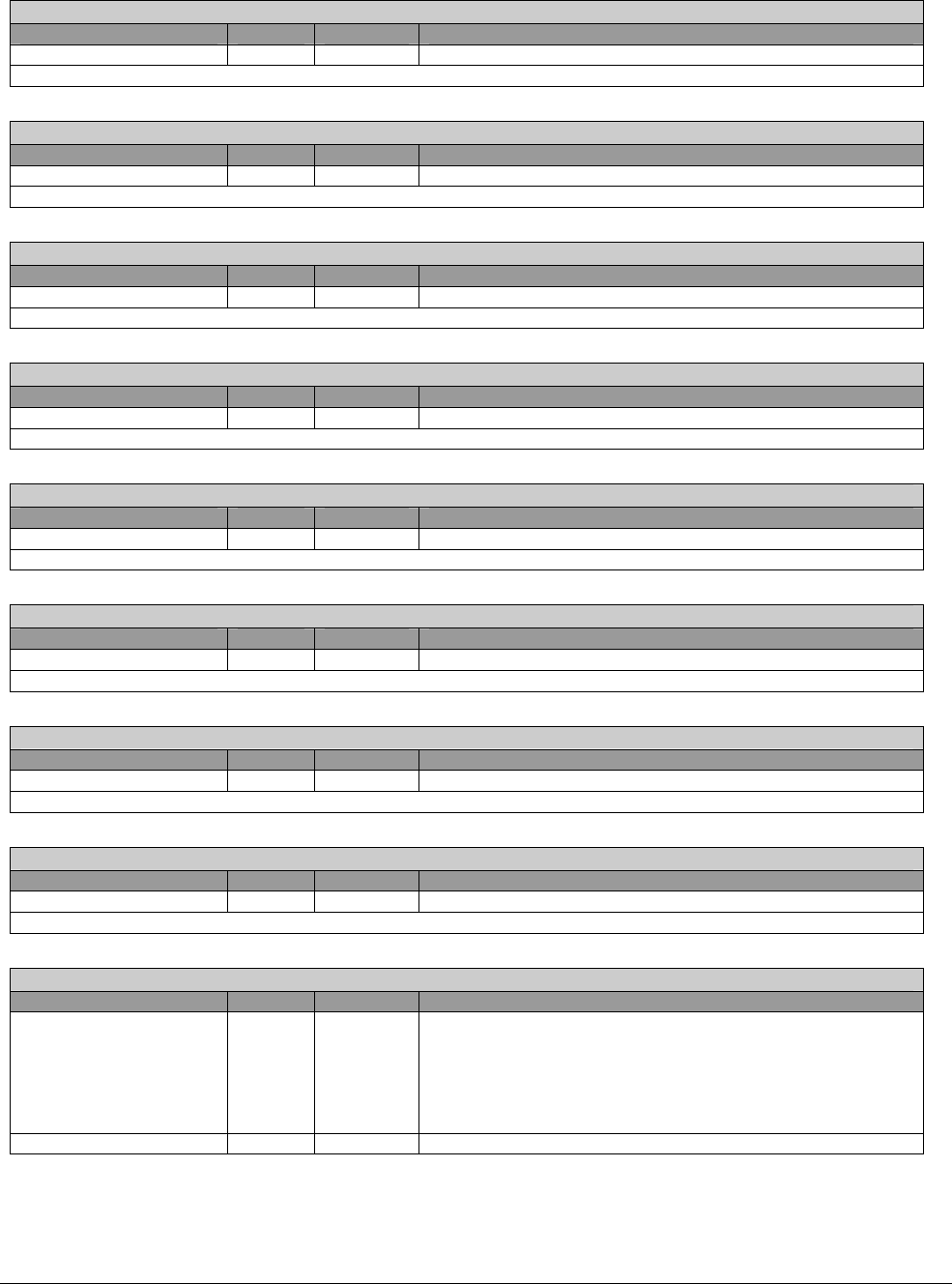

Dma_Page_Reserved4- RW – 8 bits - [IO_Reg: 88h]

Field Name Bits Default Description

Dma_Page_Reserved4 7:0 00h Dma Page Reserved4 register

Dma_Page_Reserved4 register

Dma_PageCh6 - RW – 8 bits - [IO_Reg: 89h]

Field Name Bits Default Description

Dma_PageCh6 7:0 00h DMA2 ch 6 page register

Dma_PageCh6 register

Dma_PageCh7 - RW – 8 bits - [IO_Reg: 8Ah]

Field Name Bits Default Description

Dma_PageCh7 7:0 00h DMA2 ch 7 page register

Dma_PageCh7 register

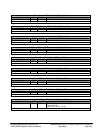

Dma_PageCh5 - RW – 8 bits - [IO_Reg: 8Bh]

Field Name Bits Default Description

Dma_PageCh5 7:0 00h DMA2 ch 5 page register

Dma_PageCh5 register

Dma_Page_Reserved5- RW – 8 bits - [IO_Reg: 8Ch]

Field Name Bits Default Description

Dma_Page_Reserved5 7:0 00h Dma Page Reserved5 register

Dma_Page_Reserved5 register

Dma_Page_Reserved6- RW – 8 bits - [IO_Reg: 8Dh]

Field Name Bits Default Description

Dma_Page_Reserved6 7:0 00h Dma Page Reserved6 register

Dma_Page_Reserved6 register

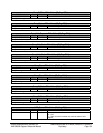

Dma_Page_Reserved7- RW – 8 bits - [IO_Reg: 8Eh]

Field Name Bits Default Description

Dma_Page_Reserved7 7:0 00h Dma Page Reserved7 register

Dma_Page_Reserved7 register

Dma_Refresh- RW – 8 bits - [IO_Reg: 8Fh]

Field Name Bits Default Description

Dma_Refresh 7:0 00h DMA2 ch4 page register.

Dma_Refresh register

FastInit- RW – 8 bits - [IO_Reg: 92h]

Field Name Bits Default Description

FastInit 0 0b FAST_INIT. This read/write bit provides a fast software

executed processor reset function. Writing

a 1 to this bit will cause the INIT assertion for approximately

4ms.

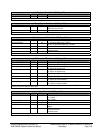

Before another INIT pulse can be generated via this register,

this bit must be written back to a 0.

A20EnB 1 0b A20Enable Bar bit; if set to 1, A20M is disabled.