©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual Proprietary Page 210

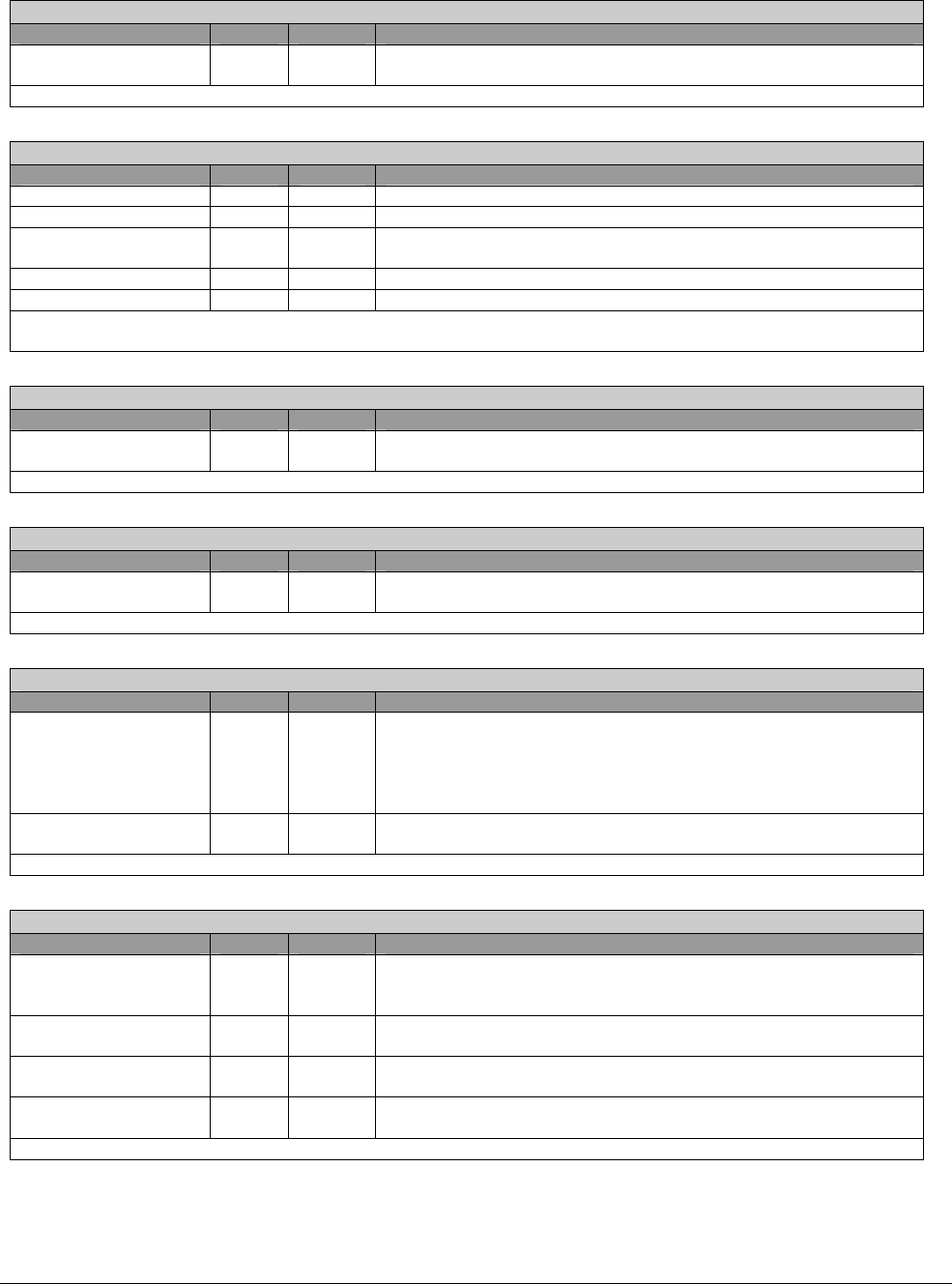

SPDIF Channel DT Current- R - 32 bits - [MEM_Reg: 5Ch]

Field Name Bits Default Description

SPDIF DT current 31:0 0000_0

000h

SPDIF Channel currently accessed memory address.

SPDIF DT Current Pointer Register: Pointer to the currently accessing memory address for the SPDIF channel.

SPDIF DT Size- R - 32 bits - [MEM_Reg: 60h]

Field Name Bits Default Description

SPDIF DT size 15:0 0000h Data size of DT for SPDIF channel.

SPDIF Used 20:16 00h Number of filled FIFO entries of SPDIF channel. Default is 0.

SPDIF Free 25:21 1Eh Number of free FIFO entries of SPDIF channel. Default is 30 (Size

of FIFO)

SPDIF DMA state 28:26 0h Current state of SPDIF DMA

Reserved 31:29 0h

SPDIF DT Size and FIFO Used/Free Register: Size of data associated with DT for SPDIF channels. Plus Number of

free and filled FIFO entries of SPDIF channel.

Modem Mirror- R - 32 bits - [MEM_Reg: 7Ch]

Field Name Bits Default Description

Modem Mirror 31:0 0000_0

000h

Data written by modem for communication with Audio.

Modem Mirror Register:

Audio Mirror- RW - 32 bits - [MEM_Reg: 80h]

Field Name Bits Default Description

Audio Mirror 31:0 0000_0

000h

Data written by audio for communication with modem. Bit 1 is used

by the BIOS to communicate with the audio driver.

Audio mirror Register:

6-Channel Reorder Enable- RW - 32 bits - [MEM_Reg: 84h]

Field Name Bits Default Description

Reorder enable 0 0 When audio output has all the 6 channels enabled, usually software

puts data in the memory using the order of 346789, and AC97

controller sends data out with the same order 346789. If software

uses the order of 346978, with this bit enabled, AC97 controller can

still send data out with the correct order 346789.

Reserved 31:1 0000_0

000h

6-Channel Reorder Enable Register

Audio Fifo Flush- W - 32 bits - [MEM_Reg: 88h]

Field Name Bits Default Description

Flush output audio fifo 0 0b Writing to this bit will flush audio output DMA fifo, i.e., the fifo

indexes and Used/Free counts will be reset. Reading this bit returns

0

Flush input audio fifo 1 0b Writing to this bit will flush audio input DMA fifo, i.e., the fifo indexes

and Used/Free counts will be reset. Reading this bit returns 0

Flush spdif fifo 2 0b Writing to this bit will flush spdif output DMA fifo, i.e., the fifo indexes

and Used/Free counts will be reset. Reading this bit returns 0

Reserved 31:3 0000_0

000h

Audio Fifo Flush Register: