©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 78

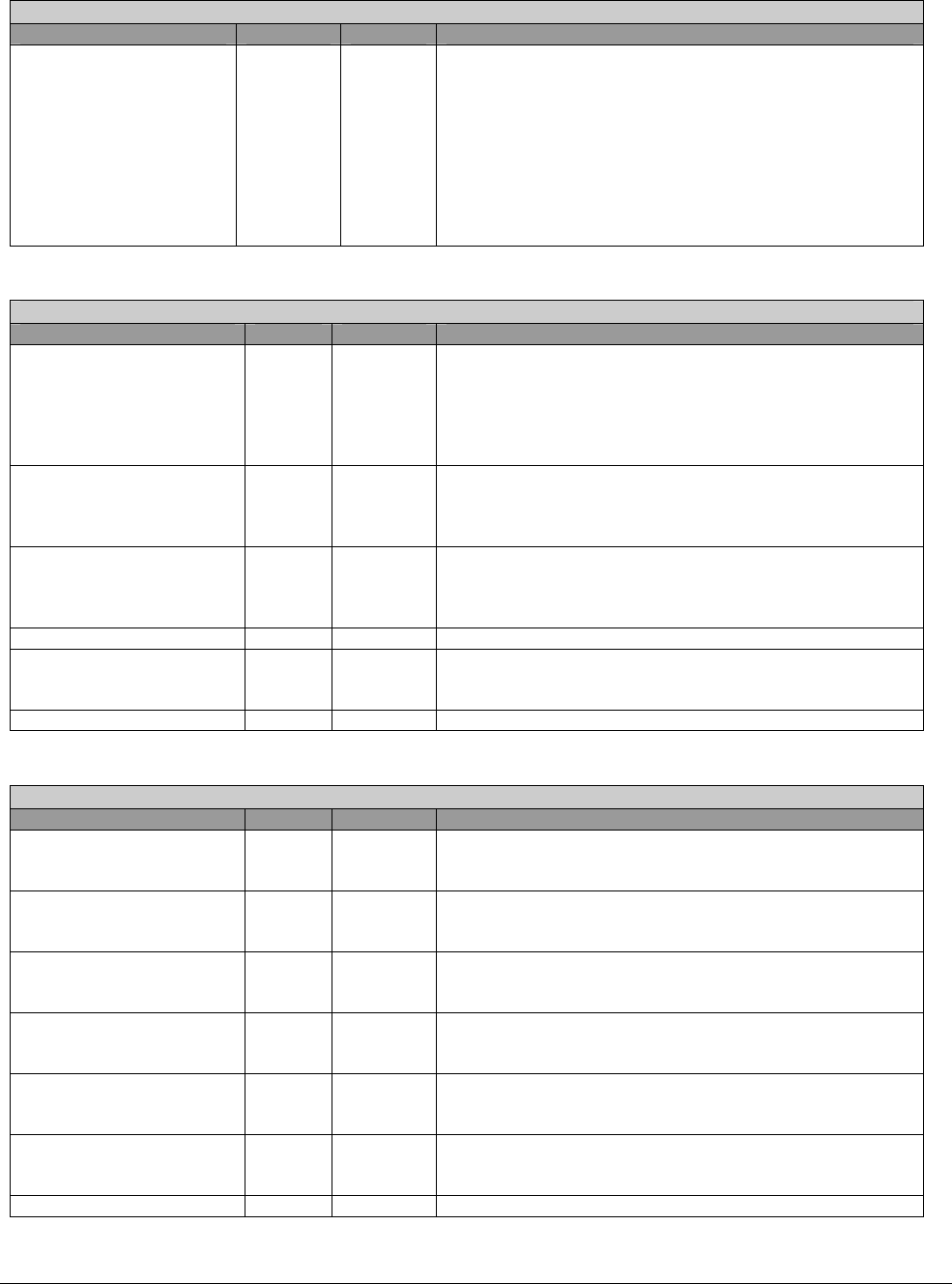

DBUG_PRT Control – R - 32 bits - [PCI_Reg : E4h]

Field Name Bits Default Description

Bar # 31:29 1h A 3-bit field, which indicates which one of the possible 6

Base Address Register offsets, contains the Debug Port

registers. For example, a value of 1h indicates the first BAR

(offset 10h) while a value of 5 indicates that the BAR at 20h.

This offset is independent as to whether the BAR is 32 or 64

bit. For example, if the offset were 3 indicating that the BAR

at offset 18h contains the Debug Port. BARs at offset 10 and

14h may or may not be implemented. This field is read only

and only values 1-6h are valid. (A 64-bit BAR is allowed.)

Only a memory BAR is allowed.

USBLEGSUP – RW - 32 bits - [PCI_Reg : EECP + 00h]

Field Name Bits Default Description

Capability ID 7:0 01h This field identifies the extended capability. A value of 01h

identifies the capability as Legacy Support. This extended

capability requires one additional 32-bit register for

control/status information, and this register is located at

offset EECP+04h.

Read Only.

Next EHCI Extended

Capability Pointer

15:8 00h This field points to the PCI configuration space offset of the

next extended capability pointer. A value of 00h indicates

the end of the extended capability list.

Read Only.

HC BIOS Owned

Semaphore

16 0b The BIOS sets this bit to establish ownership of the EHCI

controller. System BIOS will set this bit to a zero in

response to a request for ownership of the EHCI controller

by system software.

Reserved 23:17 These bits are reserved and must be set to zero.

HC OS Owned Semaphore 24 0b System software sets this bit to request ownership of the

EHCI controller. Ownership is obtained when this bit reads

as one and the HC BIOS Owned Semaphore bit reads as 0.

Reserved 31:25 These bits are reserved and must be set to zero.

USBLEGCTLSTS – RW - 32 bits - [PCI_Reg : EECP + 04h]

Field Name Bits Default Description

USB SMI Enable 0 0b When this bit is a one, and the SMI on USB Complete bit

(above) in this register is a one, the host controller will issue

an SMI immediately.

SMI on USB Error Enable 1 0b When this bit is a one, and the SMI on USB Error bit (above)

in this register is a one, the host controller will issue an SMI

immediately.

SMI on Port Change

Enable

2 0b When this bit is a one, and the SMI on Port Change Detect

bit (above) in this register is a one, the host controller will

issue an SMI immediately.

SMI on Frame List Rollover

Enable R/W

3 0b When this bit is a one, and the SMI on Frame List Rollover

bit (above) in this register is a one, the host controller will

issue an SMI immediately.

SMI on Host System Error

Enable

4 0b When this bit is a one, and the SMI on Host System Error bit

(above) in this register is a one, the host controller will issue

an SMI immediately.

SMI on Async Advance

Enable

5 0b When this bit is a one, and the SMI on Async Advance bit

(above) in this register is a one, the host controller will issue

an SMI immediately.

Reserved. 12:6 These bits are reserved and must be set to zero.