©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 98

Register Name Configuration Offset

IDE_GPIO_In A4h

GPIO_48_47_46_37_Cntrl A6h

GPIO_12_to_4_Cntrl A8h

SATA_Cntrl ACh

SataIntMap AFh

MSI_Mapping_Capability B0h

PcilntGpio BCh

UsbIntMap BEh

IoDrvSth C0h

I2CbusConfig D2h

I2CCommand D3h

I2CShadow1 D4h

I2Cshadow2 D5h

I2CBusRevision D6h

MSI_Weight E0h

AB_REG_BAR F0h

WakeIoAddr F4h

MwaitID F6h

MwaitSts F7h

ExtendedAddrPort F8h

ExtendedDataPort FCh

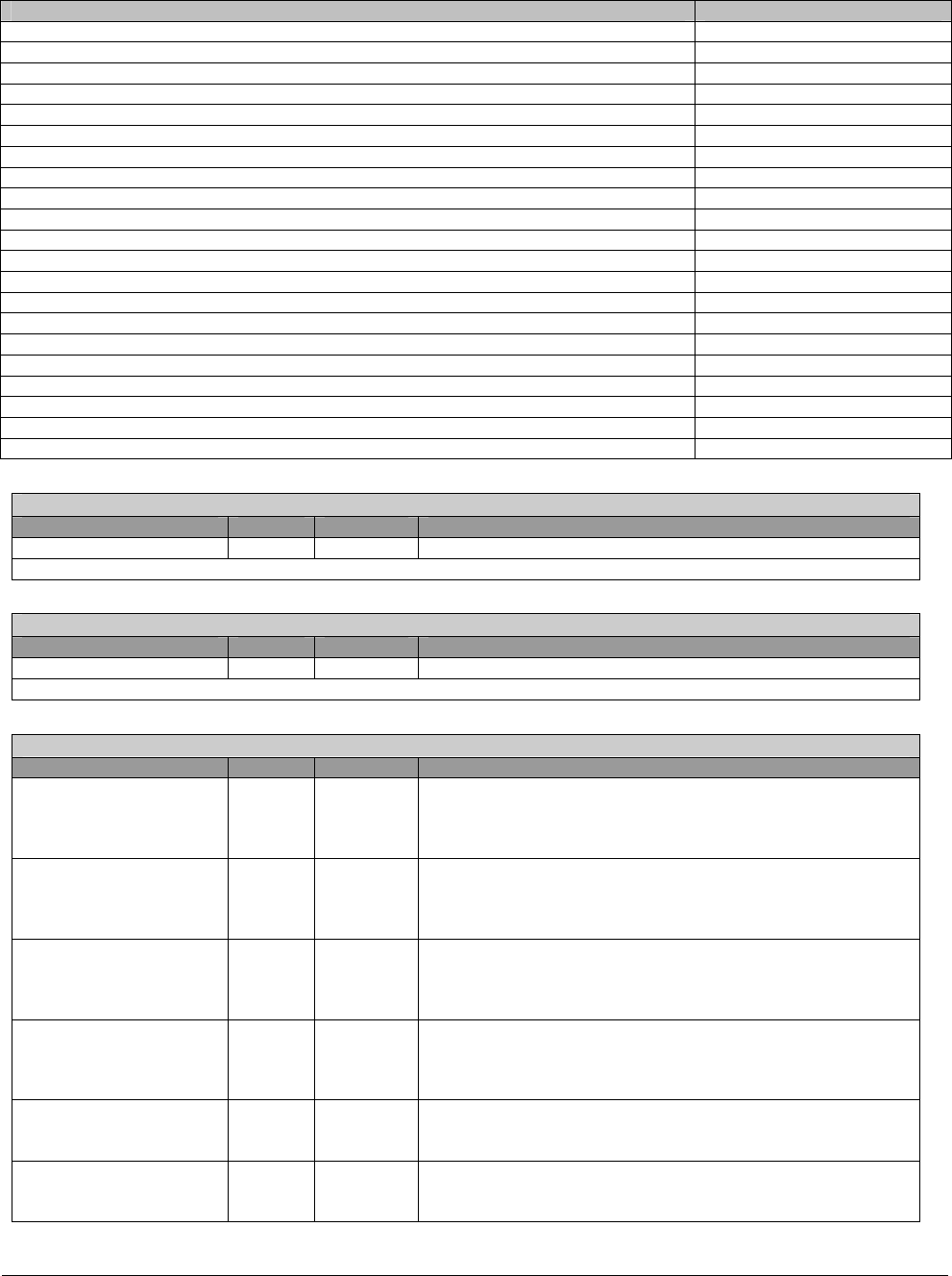

VendorID - R - 16 bits - [PCI_Reg: 00h]

Field Name Bits Default Description

VendorID 15:0 1002h Vendor ID

Vendor ID register: Vendor Identification

DeviceID - R - 16 bits - [PCI_Reg: 02h]

Field Name Bits Default Description

DeviceID 31:16 4385h Device ID

Device ID register: Device Identification Number

Command- RW - 16 bits - [PCI_Reg: 04h]

Field Name Bits Default Description

I/O Space 0 1b This bit controls a device’s response to IO space accesses. A

value of 1 enables it and a value of 0 disables it. Since this

module does claim certain legacy IO cycles, this bit is default

to 1.

Memory Space 1 1b This bit controls a device’s response to memory space

accesses. A value of 1 enables it and a value of 0 disables it.

Since this module does claim certain memory cycles if BIOS is

strapped to the PCI bus, this bit is default to 1.

Bus Master 2 0b A value of 0 disables the device from generating PCI

accesses. A value of 1 allows it to behave as a bus master.

ACPI/SMBus does not have PCI master and so it is always 0.

[Read-only]

Special Cycle 3 0b A value of 0 causes the devices to ignore all special cycle

operations. A value of 1 allows the device to monitor Special

Cycle operations. This module does not respond to special

cycle and so this is hardcoded to 0

Memory Write &

Invalidate Enable

4 0b This bit is an enable bit for using the Memory Write and

Invalidate command. This module will not generate this

command and so it is always 0. [Read-only]

VGA Palette Snoop 5 0b This bit controls how VGA compatible and graphics devices

handle accesses to VGA pallette registers. This does not

apply to this module and so it is always 0. [Read-only]