©2008 Advanced Micro Devices, Inc.

THRMTRIP/TALERT

AMD SB600 Register Reference Manual Proprietary Page 288

4.3 THRMTRIP/TALERT

4.3.1 Thermal Trip – THRMTRIP

The thermal trip function is multiplexed on the GEVENT2 pin. The THRMTRIP status cannot be used to

generate SCI or SMI#.

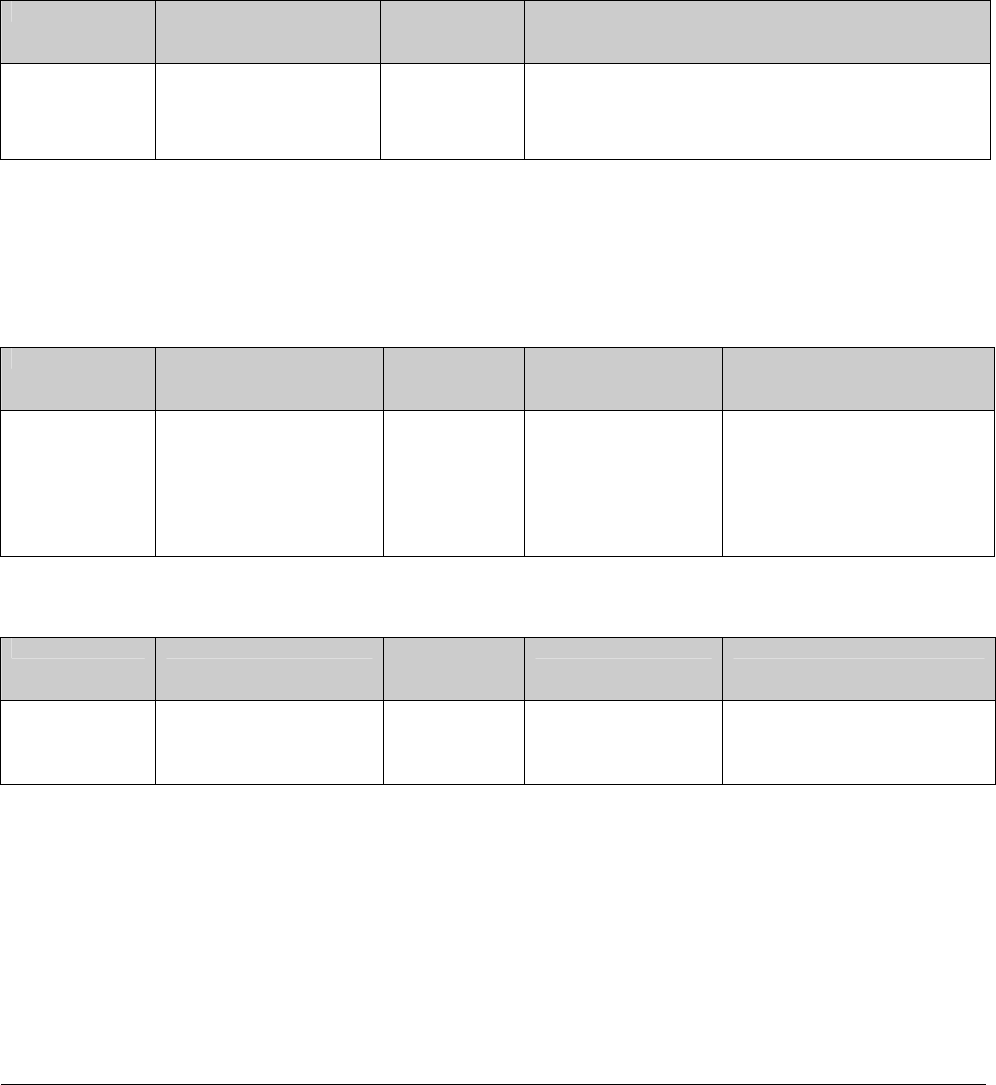

Table 4-6: THRMTRIP Pin

Pin Name Enable THRMTRIP THRMTRIP

Polarity

Control

THRMTRIP Status

THRMTRIP#/

GEVENT2#/

SMBALERT#

PM IO Reg68h[Bit 3]=1

in addition PM IO

Reg55h[Bit 0]=1 to

enable shutdown

PM IO

Reg67h[Bit 6]

0=Active Low

1=Active High

PM IO

Reg54h[Bit 0]

4.3.2 Temperature Alert – TALERT

The temperature alert function is multiplexed on the GPIO64 pin. It can be programmed to generate SMI#,

SCI, or IRQ13 through GPE. It can also be programmed to generate SMI# without using GPE.

Table 4-7: TALERT# through GPE

Pin Name TALERT# Enable TAERLT#

Polarity

Control

TALERT# Status TALERT# Outcome

TALERT#/

GPIO64/

TEMPIN3

AcpiGpe0Blk04[Bit 9]=1 PM IO

Reg67h[Bit 5]

0=Active Low

1=Active High

AcpiGpe0Blk00[Bit 9] Controlled by

PM I/O Reg3Ch[Bit3:2]:

00= ACPI Event (SCI or SMI#,

depending on SCI_EN bit)

01= SMI#

10= N/A

11= IRQ13

Table 4-8: TALERT# to generate SMI#

Pin Name TALERT# SMI# Enable TAERLT#

Polarity

Control

TALERT# Status TALERT# Outcome

TALERT#/

GPIO64/

TEMPIN3

IO C50h/C51h, index 03h

[Bit 1]=1

PM IO

Reg67h[Bit 5]

0=Active Low

1=Active High

IO C50h/C51h, index

02h [Bit 0]

SMI#