©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 111

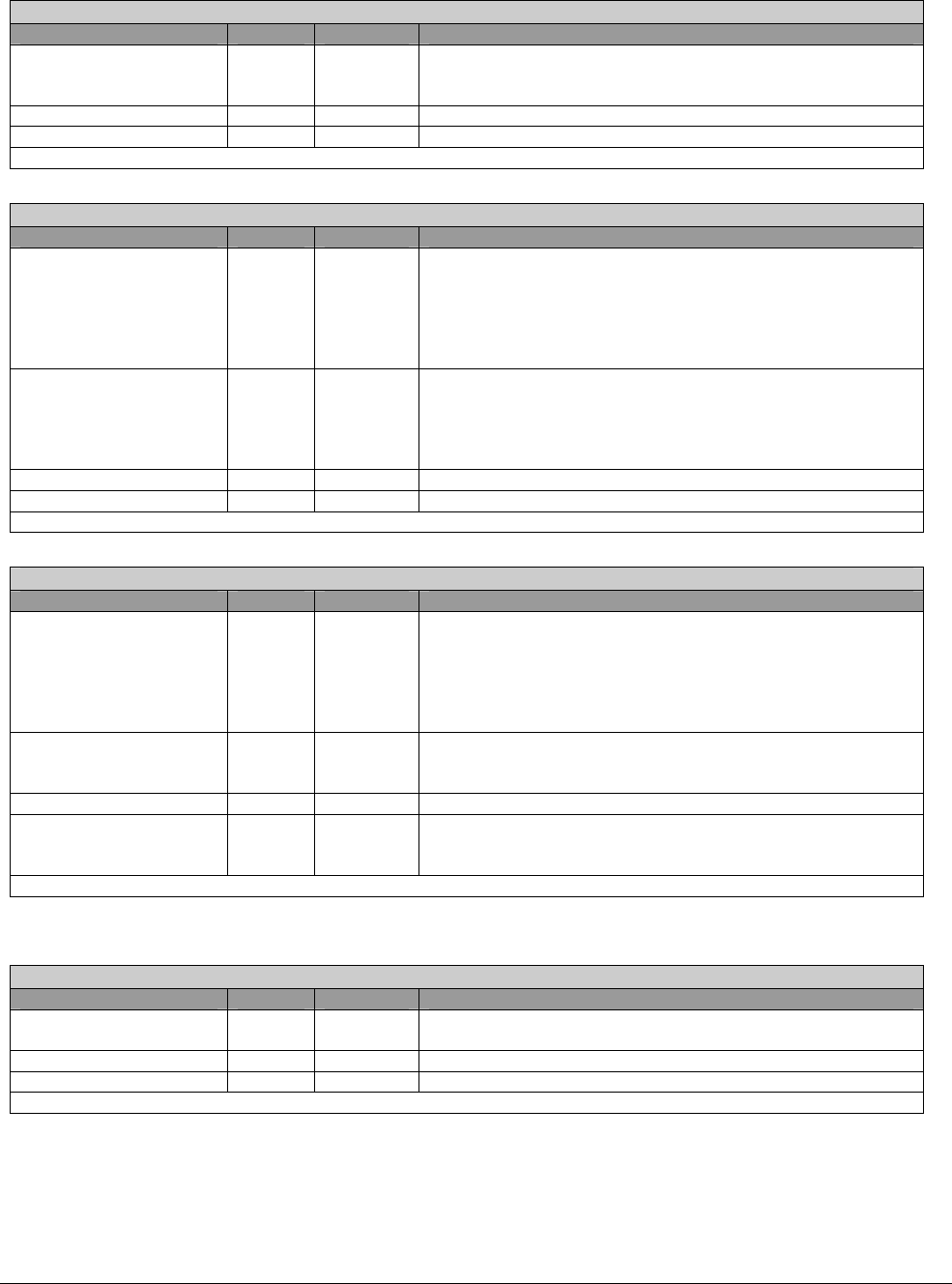

GPIO_69_68_66_65_Cntrl - RW – 16 bits - [PCI_Reg: 7Eh]

Field Name Bits Default Description

GPIO_Out_En# 7:4 Fh GPIO output port enable for each of the GPIO port

0: Output = GPIO_Out

1: Output = tristate

GPIO_Status 11:8 - GPIO input status for each of the GPIO port

Reserved 15:12 0h

GPIO_69_68_66_65_Cntrl register

GPIO_3_to_0_Cntrl - RW – 16 bits - [PCI_Reg: 80h]

Field Name Bits Default Description

GPIO_Out 3:0 0h Write 1 to set and 0 to clear each of the GPIO port providing

the corresponding bits [7:4] are enabled

Bit[0] for GPIO0/ SSMUXSEL

Bit[1] for GPIO1/ROM_CS#

Bit[2] for GPIO2/SPKR

Bit[3] for GPIO3/FANOUT0

GPIO_Out_En# 7:4 Fh GPIO output port enable for each of the GPIO port

0: Output = GPIO_Out

1: Output = tristate

For GPIO1, this is applicable only if we are not using the

external PCI bus as the ROM interface.

GPIO_Status 11:8 - GPIO input status for each of the GPIO port

Reserved 15:12 0h

GPIO_3_to_0_Cntrl register

GPIO_32_31_14_13_Cntrl - RW – 16 bits - [PCI_Reg: 82h]

Field Name Bits Default Description

GPIO_Out 3:0 0h Write 1 to set and 0 to clear each of the GPIO port providing

the corresponding bits [7:4] and [15:12] are enabled

Bit[0] for GPIO13/LAN_RST#

Bit[1] for GPIO14/ROM_RST#

Bit[2] for GPIO31/SPI_HOLD#

Bit[3] for GPIO32/SPI_CS#

GPIO_Out_En# 7:4 Fh GPIO output port enable for each of the GPIO port

0: Output = GPIO_Out

1: Output = tristate

GPIO_Status 11:8 - GPIO input status for each of the GPIO port

GPIO_Enable 15:12 0h GPIO function enable for each of the GPIO port

0: GPIO disabled

1: GPIO enabled

GPIO_32_31_14_13_Cntrl register

Smbus Base Address - R – 32 bits - [PCI_Reg: 90h]

Field Name Bits Default Description

IO/Memory 0 1b 1 = IO

0 = Memory

Reserved 3:1 000b

SmBusBaseAd 31:4 0000000h SMBus Base Address

Smbus Base Address register (also accessible through 10h)